## Digital Control of a Class-D Audio Amplifier

by

Jason Quibell

Thesis submitted in fulfilment of the requirements for the degree Master of Technology: Electrical Engineering in the Faculty of Engineering at the Cape Peninsula University of Technology

> Supervisor: Prof. R.H. Wilkinson Co-supervisor: Prof. H. du T. Mouton

> > Cape Town, South Africa November 2011

# Declaration

| I, Jason Quibell, declare that the contents of this thesis represent my own  |

|------------------------------------------------------------------------------|

| unaided work, and that the thesis has not previously been submitted for aca- |

| demic examination towards any qualification. Furthermore, it represents my   |

| own opinions and not necessarily those of the Cape Peninsula University of   |

| Technology.                                                                  |

|                                                                              |

|                                                                              |

| Signature: |                  |

|------------|------------------|

|            |                  |

|            |                  |

| Date:      | 23 November 2011 |

Copyright  $\bigodot$  2012 Cape Peninsula University of Technology All rights reserved.

## Abstract

Modern technologies have led to extensive digital music reproduction and distribution. It is fitting then that digital audio be amplified directly from its source rather than being converted to an analogue waveform before amplification. The benefits of using a digital controller for audio processing include being able to easily reconfigure the system and to add additional functions at a later stage.

Digital audio is primarily stored as Pulse Code Modulation (PCM) while Pulse Width Modulation (PWM) is the most popular scheme used to drive a class-D amplifier. The class-D amplifier is selected in many applications due to its very high energy efficiency. Conventional PCM to PWM conversion is inherently nonlinear. Various interpolation schemes are presented in this research project which help to address the nonlinearity.

Digitally generated PWM has a limited resolution which is constrained by the system clock. This thesis presents noise shaping techniques which increase the effective resolution of the PWM process without having to use an excessively high system clock. Noise shaping allows a low resolution modulator to be used to reproduce high resolution audio.

# Acknowledgements

I would like to express my sincere gratitude to the following people and organisations:

National Research Foundation (NRF)

Cape Peninsula University of Technology (CPUT)

Centre for Instrumentation Research (CIR)

French South African Institute of Technology (F'SATI)

Professor Richardt Wilkinson for his guidance

Professor Toit Mouton for his generosity of knowledge

Mr Robert Neilson for his insightful suggestions

Professor Gerhart de Jager for his years of wisdom

Charl Jooste for his camaraderie

The financial assistance of the National Research Foundation and the Cape Peninsula University of Technology towards this research is acknowledged. Opinions expressed in this thesis and the conclusions arrived at, are those of the author, and are not necessarily to be attributed to the respective mentioned establishments.

# Dedications

To Mom, Dad, Bonnie, Tyrus, Keegan, Oliver and Gaby for their unwavering support

# Contents

| D            | eclar | ration                           | i            |

|--------------|-------|----------------------------------|--------------|

| $\mathbf{A}$ | bstra | act                              | ii           |

| $\mathbf{A}$ | ckno  | wledgements                      | iii          |

| D            | edica | ations                           | iv           |

| C            | onter | nts                              | $\mathbf{v}$ |

| Li           | st of | Figures                          | viii         |

| Li           | st of | Tables                           | xii          |

| N            | omer  | nclature                         | xiii         |

| 1            | Intr  | roduction                        | 1            |

|              | 1.1   | Background                       | . 1          |

|              | 1.2   | Problem statement                | . 1          |

|              | 1.3   | Objectives of the research       |              |

|              | 1.4   | Structure of the thesis          |              |

| <b>2</b>     | Dig   | rital signal processing          | 6            |

|              | 2.1   | DSP applications                 | . 6          |

|              | 2.2   | Signal sampling and quantisation | . 7          |

|              | 2.3   | Hardware for signal processing   | . 9          |

|              | 2.4   | Conclusion                       | . 12         |

| 3            | Pul   | se width modulation              | 13           |

|              | 3.1   | Theory of operation              | . 14         |

|              | 3.2   | Natural and uniform sampling     | . 15         |

|              | 3.3   | Harmonic distortion              | . 16         |

|              | 3.4   | Conclusion                       |              |

| 4            |       | erpolation                       | 18           |

|              | 11    | Introduction                     | 18           |

| CONTENTS | vi |  |

|----------|----|--|

|          |    |  |

|          | 4.2              | Sample rate conversion                       |      |

|----------|------------------|----------------------------------------------|------|

|          | 4.3              | Finite impulse response interpolation filter |      |

|          | 4.4              | Polyphase interpolation filter               |      |

|          | 4.5              | Cascaded integrator comb filter              |      |

|          | 4.6              | Polynomial interpolation                     |      |

|          | 4.7              | Conclusion                                   | . 39 |

| 5        | Noi              | se shaping                                   | 40   |

|          | 5.1              | Introduction                                 | . 40 |

|          | 5.2              | General noise shaping                        | . 41 |

|          | 5.3              | Digital noise shaping loop filter            |      |

|          | 5.4              | Ripple compensation                          | . 60 |

|          | 5.5              | Ripple compensation verification             | . 62 |

|          | 5.6              | Loop filter implementation                   |      |

|          | 5.7              | Conclusion                                   | . 77 |

| 6        | VH               | DL Implementation                            | 78   |

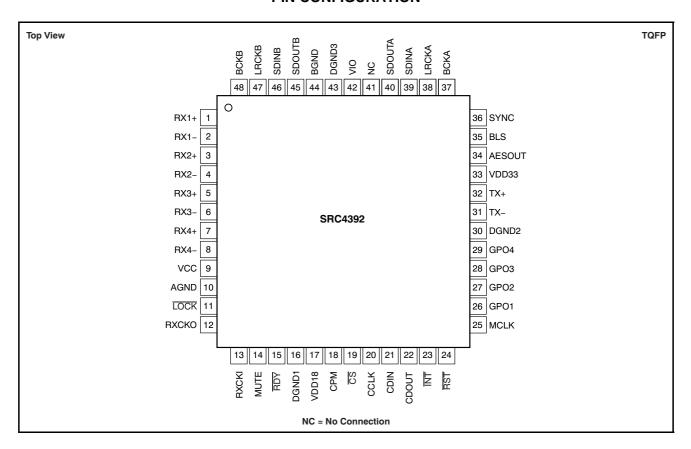

|          | 6.1              | Hardware interconnections                    | . 79 |

|          | 6.2              | Configuration                                | . 80 |

|          | 6.3              | Receive audio data                           | . 84 |

|          | 6.4              | Interpolation                                | . 86 |

|          | 6.5              | Noise shaping                                | . 88 |

|          | 6.6              | Pulse width modulation and feedback          | . 90 |

|          | 6.7              | Synchronisation                              | . 91 |

|          | 6.8              | Conclusion                                   | . 91 |

| 7        | Test             | t and verification                           | 92   |

|          | 7.1              | Initial testing                              | . 92 |

|          | 7.2              | System redesign                              |      |

|          | 7.3              | Conclusion                                   |      |

| 8        | Res              | ults                                         | 97   |

|          | 8.1              | Hardware setup                               |      |

|          | 8.2              | Simulation verification                      |      |

|          | 8.3              | Measurements                                 |      |

|          | 8.4              | Conclusion                                   |      |

| 9        | Cor              | nclusion                                     | 108  |

| -        | 9.1              | Overview of project objectives               |      |

|          | 9.2              | Objectives achieved                          |      |

|          | 9.3              | Problems encountered                         |      |

|          | 9.4              | Future research and recommendations          |      |

| ${f Li}$ | $\mathbf{st}$ of | References                                   | 111  |

| CONTENTS | vii |

|----------|-----|

|          |     |

| Aŗ           | pen  | dices                                                                  | 114        |

|--------------|------|------------------------------------------------------------------------|------------|

| $\mathbf{A}$ |      | se shaper filter coefficients  Classic noise shaper coefficient design | 115<br>115 |

| В            | VH   | DL source code                                                         | 117        |

|              | B.1  | Main program source code                                               | 117        |

|              | B.2  | SPI source code                                                        | 124        |

|              | B.3  | Receive audio data source code                                         | 127        |

|              | B.4  | Interpolation source code                                              | 131        |

|              | B.5  | Noise shaper source code                                               | 139        |

|              | B.6  | Pulse Width Modulation source code                                     | 146        |

| $\mathbf{C}$ | Mat  | lab source code                                                        | 149        |

|              | C.1  | Interpolation                                                          | 149        |

|              | C.2  | Polynomial interpolation                                               |            |

|              | C.3  | Noise shaper filter coefficient calculator                             |            |

|              | C.4  | Modulation                                                             | 161        |

|              | C.5  | Spectral content                                                       | 164        |

| D            | Data | a sheets                                                               | 165        |

|              | D.1  | SRC4392                                                                | 165        |

|              | D.2  | Altera Cyclone III (EP3C25)                                            |            |

# List of Figures

| 2.1               | Correct sampling which will not result in aliasing adapted from Tan (2008)                                       | 8               |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.2<br>2.3<br>2.4 | Incorrect sampling which leads to aliasing adapted from Tan (2008) Floating point format adapted from Tan (2008) | 9<br>11<br>12   |

| 3.1<br>3.2        | Archetype pulse width modulator                                                                                  | 13<br>14        |

| 3.3               | UPWM and NPWM producing different PWM waveforms adapted from Nielsen (1998) and Jacobs (2006)                    | 15              |

| 4.1               | Upsampler                                                                                                        | 19              |

| 4.2               | Sine wave before and after upsampling                                                                            | 20              |

| 4.3               | 1 kHz sine wave spectrum before and after upsampling                                                             | 21              |

| 4.4               | Upsampler with low-pass filter                                                                                   | 22              |

| 4.5               | FIR filter magnitude and phase response                                                                          | 24              |

| 4.6               | 1 kHz sine wave spectrum before and after being filtered                                                         | 24              |

| 4.7               | Direct interpolation filter                                                                                      | 25              |

| 4.8               | Polyphase filter implementation adapted from Tan (2008)                                                          | 26              |

| 4.9               | Commutative model for the polyphase interpolation filter adapted                                                 |                 |

|                   | from Tan (2008)                                                                                                  | 26              |

|                   | Impulse response of the original FIR filter                                                                      | 27              |

|                   | Impulse response of the first polyphase filter                                                                   | 28              |

|                   | Impulse response of the second polyphase filter                                                                  | 28              |

|                   | CIC filter block diagram adapted from Hogenauer (1981)                                                           | 30<br>32        |

|                   | 9 1                                                                                                              | $\frac{32}{32}$ |

|                   | CIC compensation filter block diagram                                                                            | 33              |

|                   | Magnitude response of a CIC filter cascaded with a CIC compensator                                               |                 |

|                   | Curve constructed from discrete data points                                                                      | 35              |

|                   | Unstable curve constructed from 11 data points                                                                   | 38              |

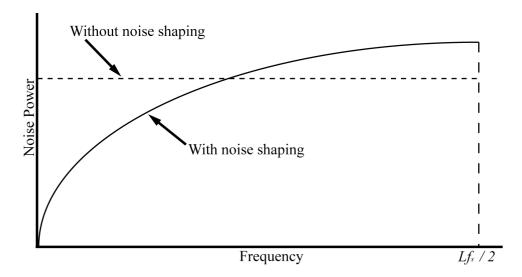

| 5.1               | Shaped and unshaped noise adapted from Craven (1993)                                                             | 41              |

LIST OF FIGURES ix

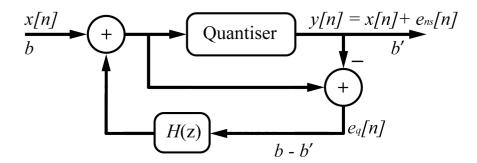

| 5.2  | Noise shaper configuration adapted from Goldberg & Sandler (1991a)                                                         | 42 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

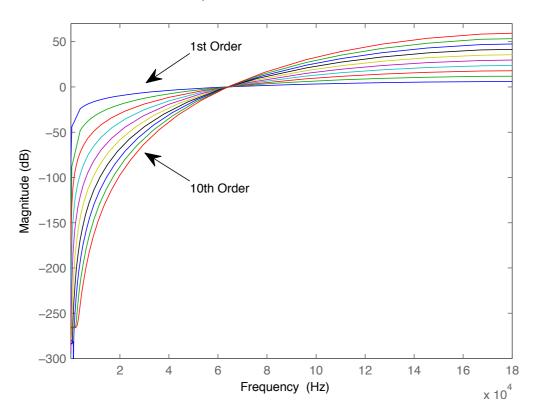

| 5.3  | Noise shaping filter when calculated for different orders adapted                                                          |    |

|      | from Hawksford (1989 $a$ ) and Jacobs (2006)                                                                               | 43 |

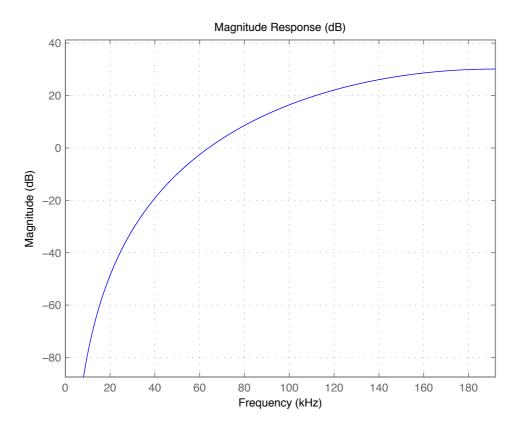

| 5.4  | Magnitude response of a fifth order filter using calculated coefficients                                                   | 44 |

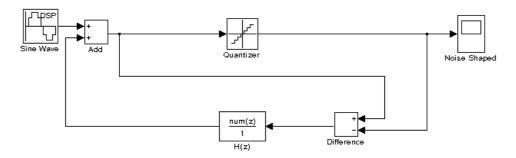

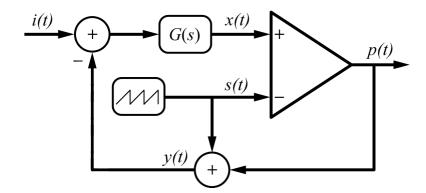

| 5.5  | Noise shaper Simulink model                                                                                                | 45 |

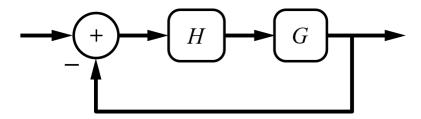

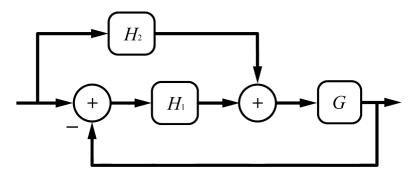

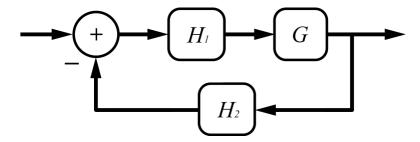

| 5.6  | Cascade compensation adapted from Wescott (2006)                                                                           | 46 |

| 5.7  | Feedforward compensation adapted from Wescott (2006)                                                                       | 46 |

| 5.8  | Feedback compensation adapted from Wescott (2006)                                                                          | 47 |

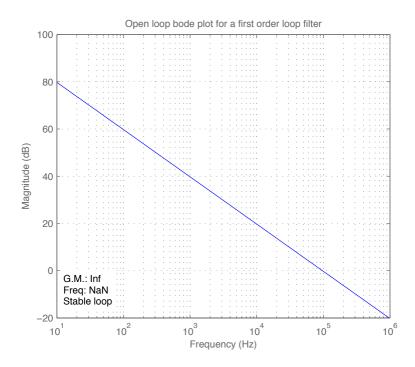

| 5.9  | Open loop bode plot for a first order filter                                                                               | 48 |

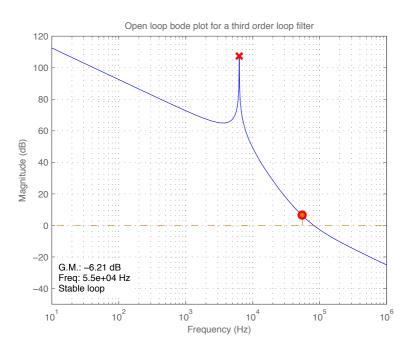

| 5.10 | Open loop bode plot of a third order filter                                                                                | 49 |

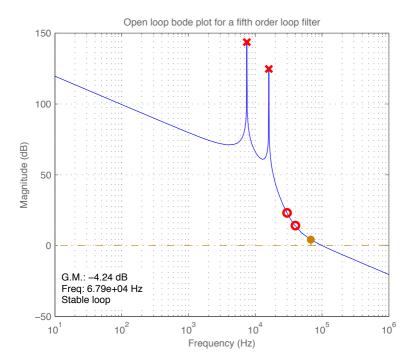

| 5.11 | Open loop bode plot of a fifth order filter                                                                                | 50 |

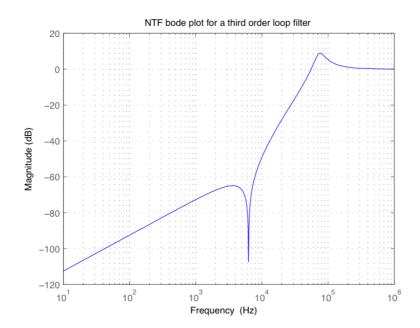

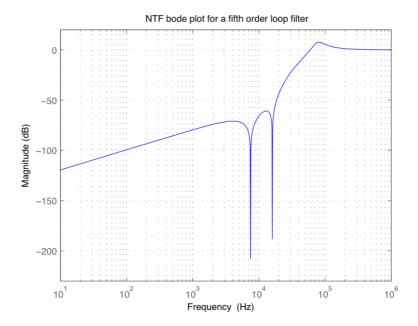

| 5.12 | NTF bode plot of a third order filter                                                                                      | 51 |

| 5.13 | NTF bode plot of a fifth order filter                                                                                      | 51 |

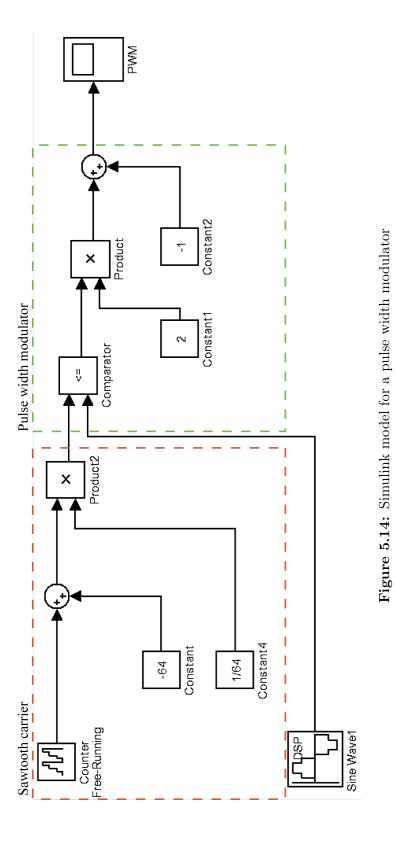

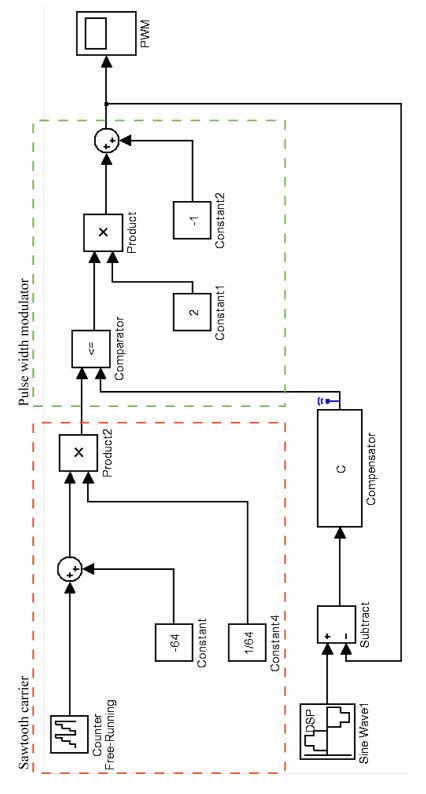

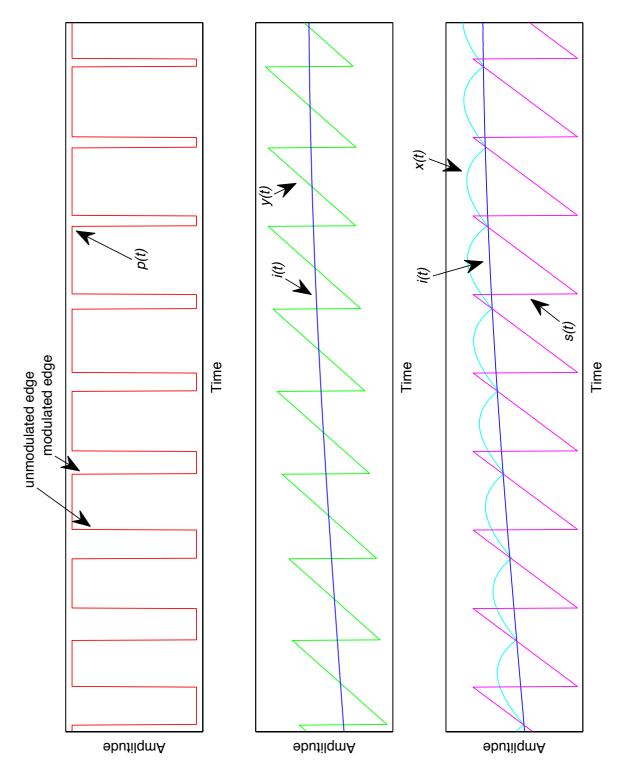

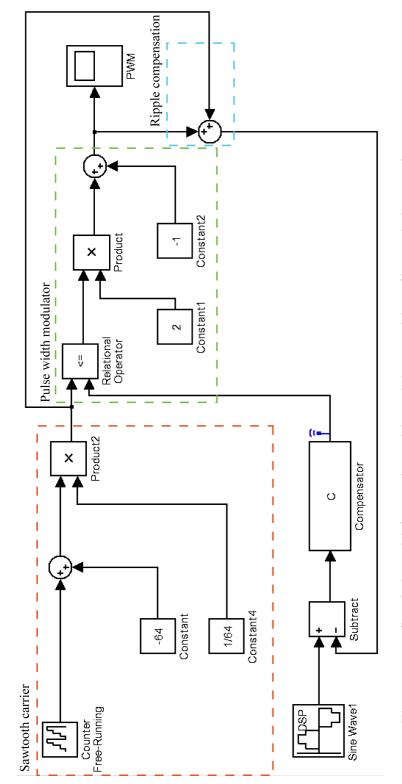

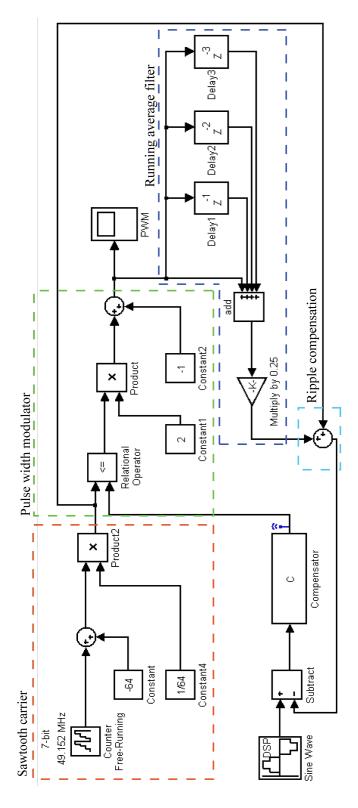

| 5.14 | Simulink model for a pulse width modulator                                                                                 | 53 |

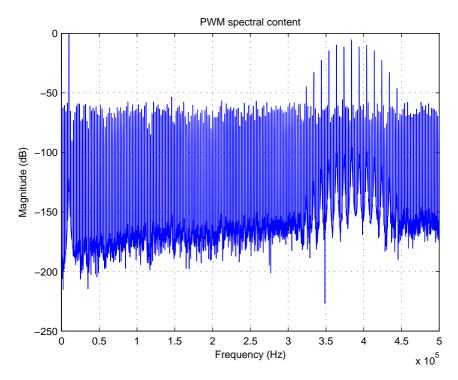

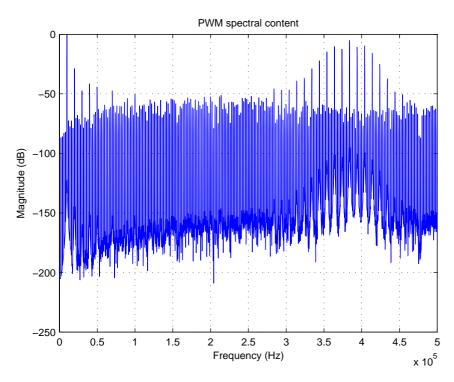

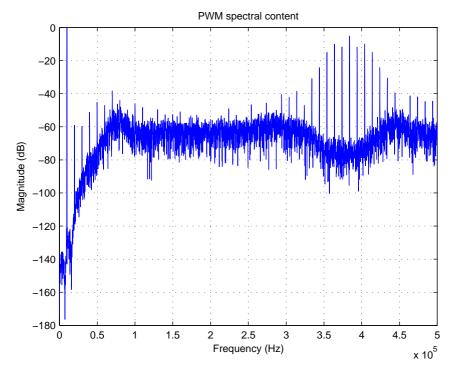

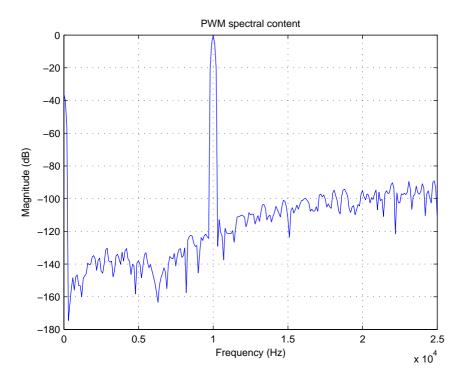

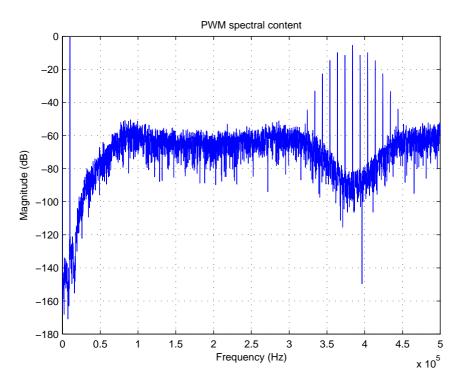

| 5.15 | Spectral content of a 7-bit PWM waveform                                                                                   | 54 |

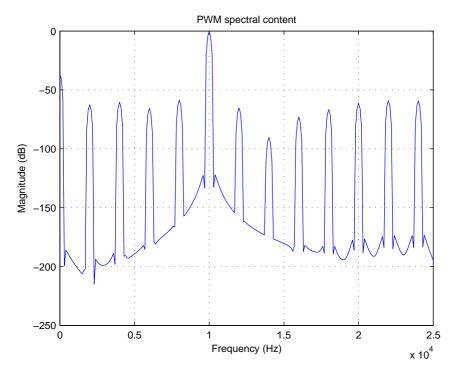

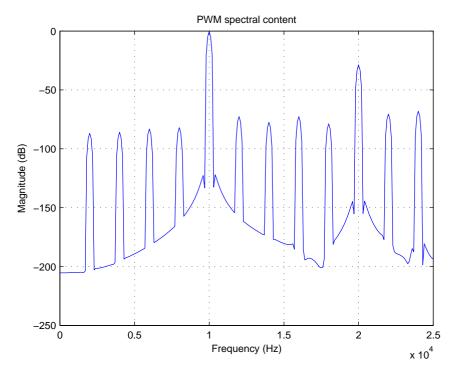

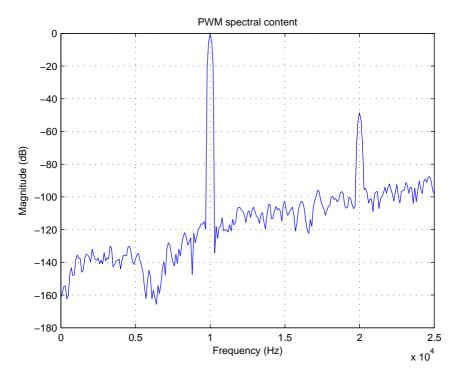

| 5.16 | Zoomed view of the audio band of Figure 5.15                                                                               | 54 |

| 5.17 | Simulink model for a pulse width modulator and loop filter                                                                 | 55 |

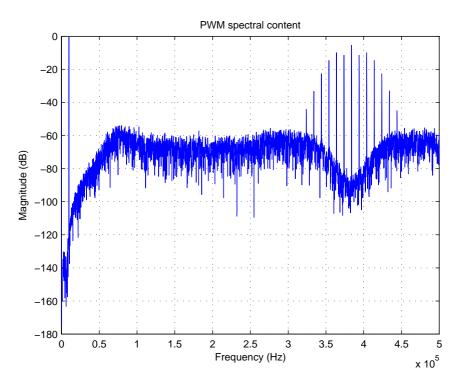

| 5.18 | Spectral content of a 7-bit PWM waveform with a first order filter .                                                       | 56 |

| 5.19 | Zoomed view of the audio band of Figure 5.18                                                                               | 56 |

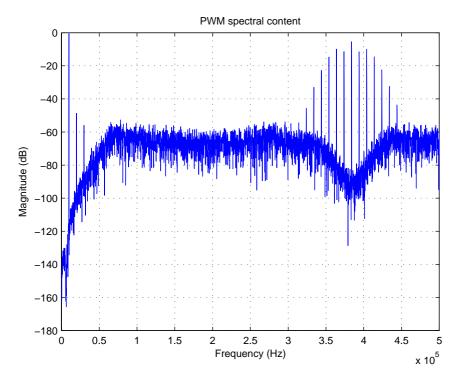

| 5.20 | Spectral content of a 7-bit PWM waveform with a third order loop                                                           |    |

|      | filter                                                                                                                     | 57 |

| 5.21 | Spectral content of a 7-bit PWM waveform with a fifth order loop                                                           |    |

|      | filter                                                                                                                     | 57 |

| 5.22 | Zoomed view of the audio band of Figure 5.20                                                                               | 58 |

| 5.23 | Zoomed view of the audio band of Figure 5.21                                                                               | 58 |

| 5.24 | Implementation of ripple compensation adapted from Mouton $\mathcal{E}$                                                    |    |

|      | Putzeys (2009)                                                                                                             | 62 |

| 5.25 | Ripple compensation waveforms adapted from Mouton $\operatorname{\mathscr{C}}$ Putzeys                                     |    |

|      | $(2009) \dots \dots$ | 63 |

| 5.26 | Simulink model for a pulse width modulator and loop filter includ-                                                         |    |

|      | ing ripple compensation                                                                                                    | 64 |

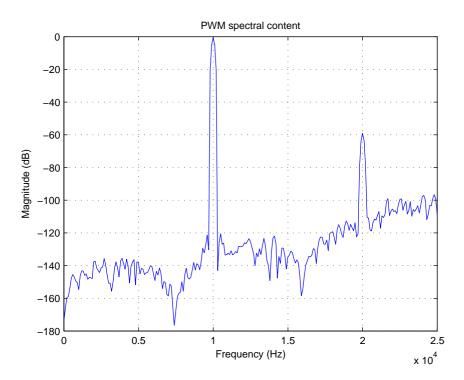

| 5.27 | Spectral content of a 7-bit PWM waveform with a third order loop                                                           |    |

|      | filter and ripple compensation                                                                                             | 65 |

| 5.28 | Zoomed view of the audio band of Figure 5.27                                                                               | 65 |

| 5.29 | Spectral content of a 7-bit PWM waveform with a fifth order loop                                                           |    |

|      | filter and ripple compensation                                                                                             | 66 |

| 5.30 | Zoomed view of the audio band of Figure 5.29                                                                               | 66 |

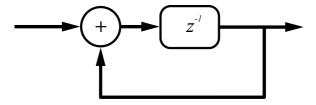

| 5.31 | Delayed output integrator                                                                                                  | 67 |

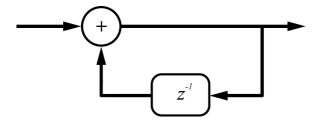

| 5.32 | Non-delayed output integrator                                                                                              | 68 |

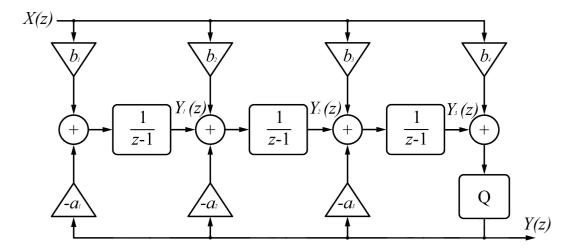

| 5.33 | Cascade of integrators with feedback summation adapted from Schreier                                                       |    |

|      | $\mathscr{C}$ Temes (2005)                                                                                                 | 68 |

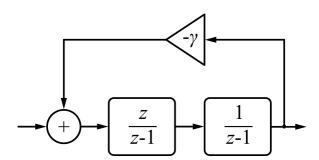

| 5.34 | Resonator for a loop filter adapted from Norsworthy et al. (1997) .                                                        | 69 |

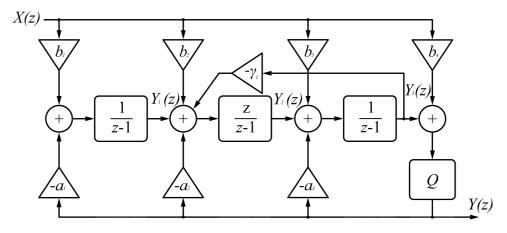

| 5.35 | Cascaded resonator with feedback summation adapted from Schreier                                                           |    |

|      | $\mathcal{E}$ Temes (2005)                                                                                                 | 70 |

LIST OF FIGURES x

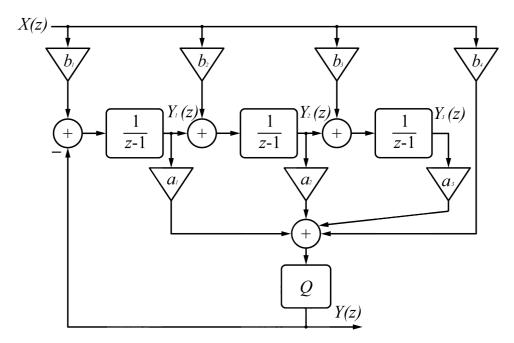

| 5.36 | Cascaded integrators with feedforward summation adapted from Schreier $\mathscr{C}$ Temes (2005)           | . 71  |

|------|------------------------------------------------------------------------------------------------------------|-------|

| 5.37 | Cascaded resonator with feedforward summation adapted from Nor-                                            |       |

| 5 20 | sworthy et al. (1997)                                                                                      |       |

|      | 1                                                                                                          |       |

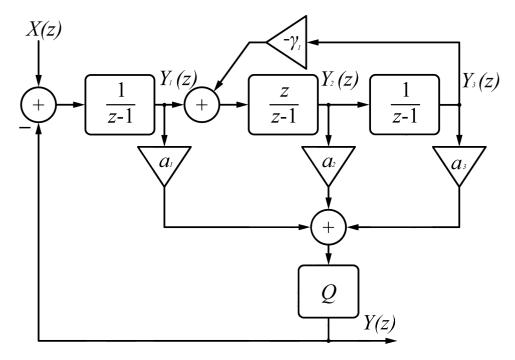

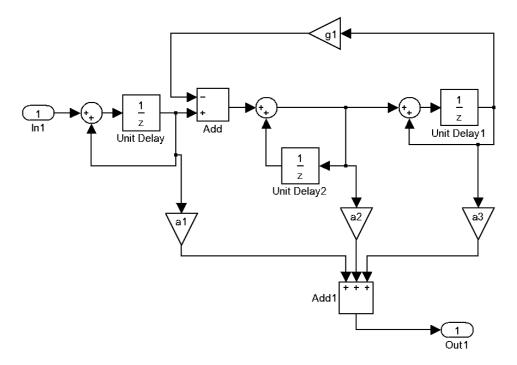

|      | Third order loop filter Simulink implementation                                                            |       |

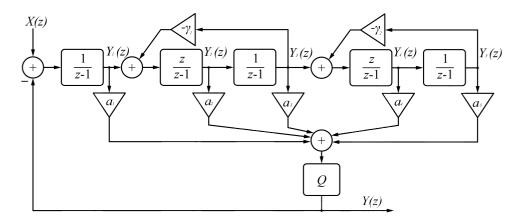

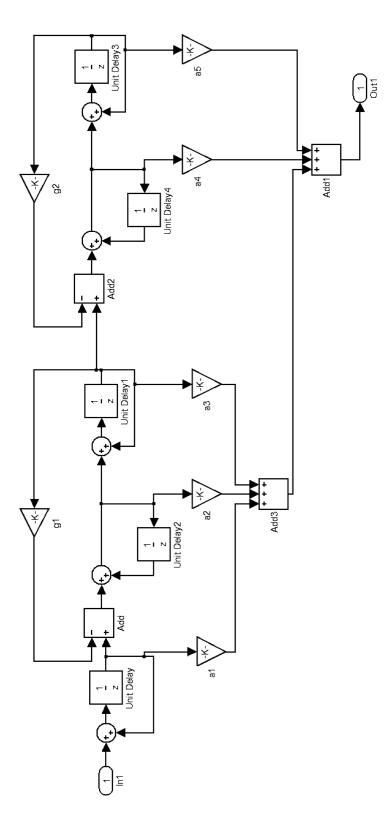

| 5.40 | Fifth order loop filter Simulink implementation                                                            | . 76  |

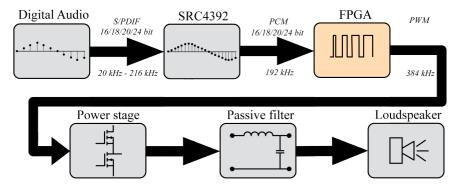

| 6.1  | Block diagram of a complete audio system                                                                   | . 79  |

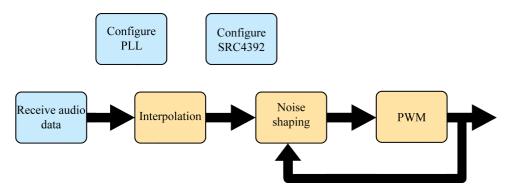

| 6.2  | Firmware block diagram                                                                                     | . 80  |

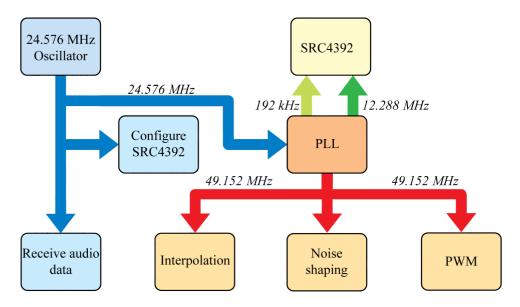

| 6.3  | PLL clock distribution                                                                                     | . 81  |

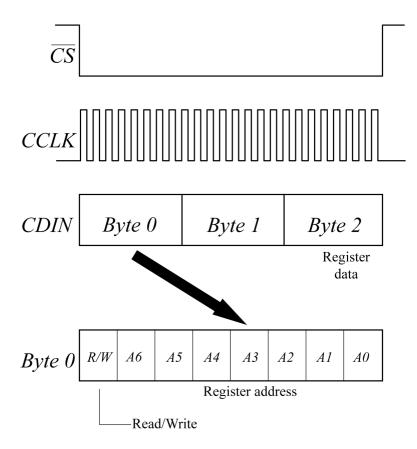

| 6.4  | Configuration via SPI                                                                                      | . 83  |

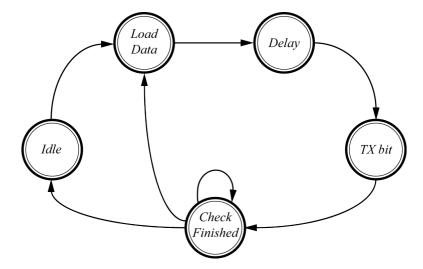

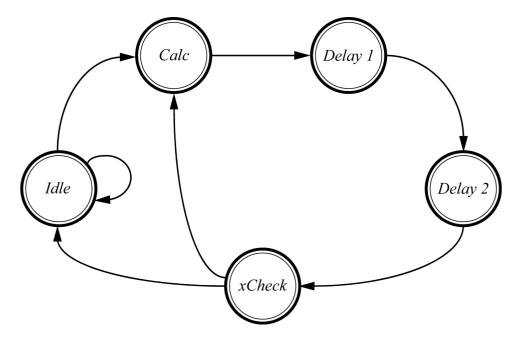

| 6.5  | SPI state diagram                                                                                          | . 84  |

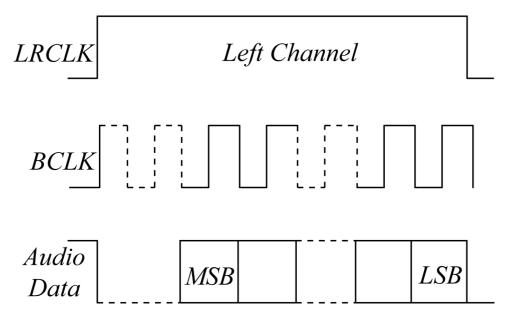

| 6.6  | Right-justified data format                                                                                | . 85  |

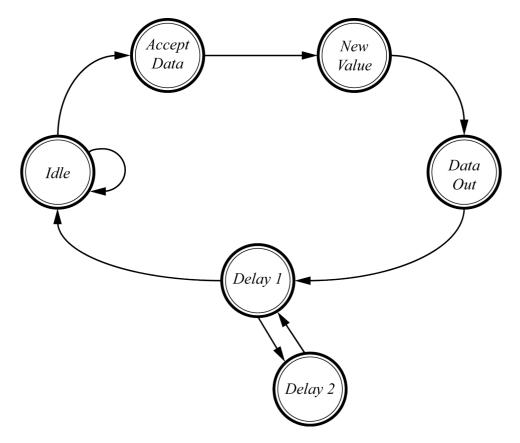

| 6.7  | Audio buffer state diagram                                                                                 |       |

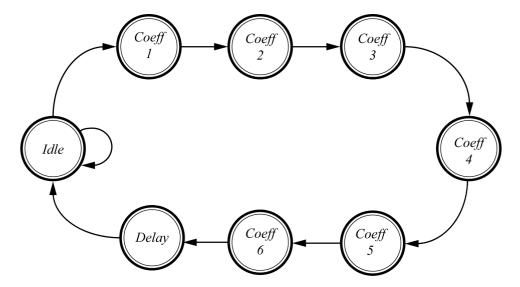

| 6.8  | Polynomial coefficients state diagram                                                                      | . 87  |

| 6.9  | Polynomial calculation state diagram                                                                       | . 88  |

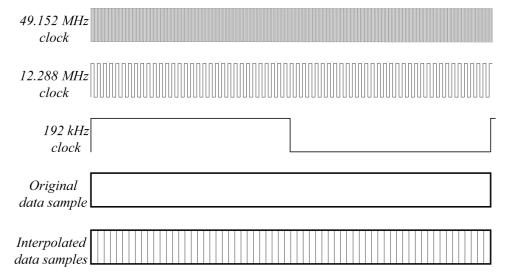

| 6.10 | Timing diagram for the sample rate conversion                                                              |       |

| 7.1  | Simulink model for a pulse width modulator and loop filter including ripple compensation and PWM averaging | . 95  |

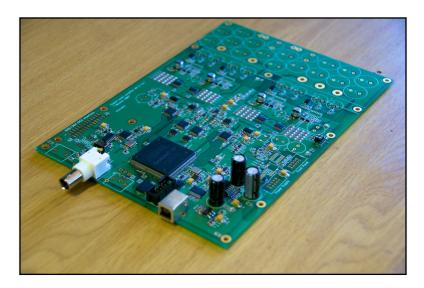

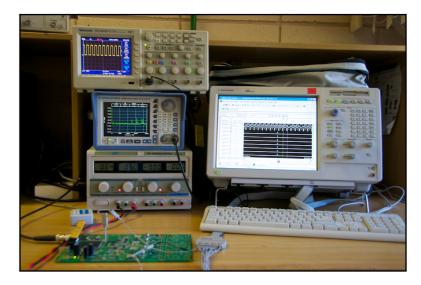

| 8.1  | FPGA based audio amplifier board                                                                           | . 97  |

| 8.2  | Hardware test instrument set up                                                                            |       |

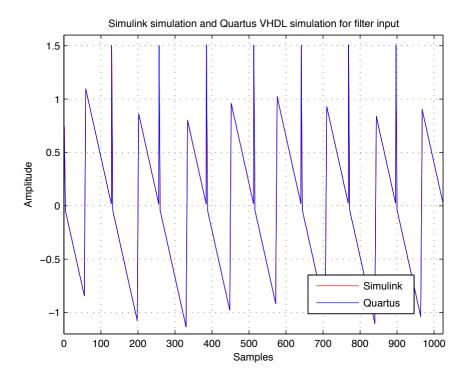

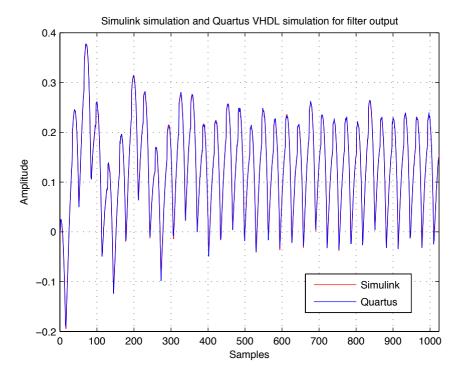

| 8.3  | Comparisson between Simulink and Quartus simulations for the                                               |       |

|      | filter input                                                                                               | . 99  |

| 8.4  | Comparisson between Simulink and Quartus simulations for the                                               |       |

|      | filter output                                                                                              | . 99  |

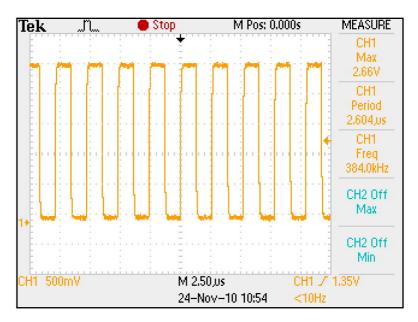

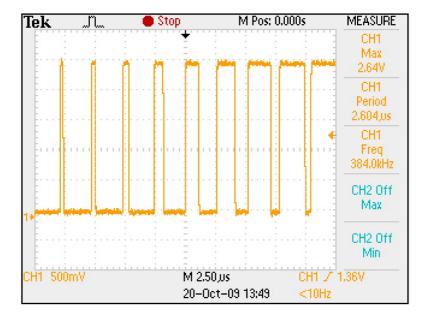

| 8.5  | PWM waveform switching at 384 kHz with a 50% duty cycle                                                    | . 100 |

| 8.6  | PWM waveform switching at 384 kHz modulated with a 20 kHz                                                  |       |

|      |                                                                                                            | . 101 |

| 8.7  | Logic analyser result of a PWM waveform switching at 384 kHz                                               |       |

|      | which has been modulated with a 20 kHz sine wave                                                           | . 101 |

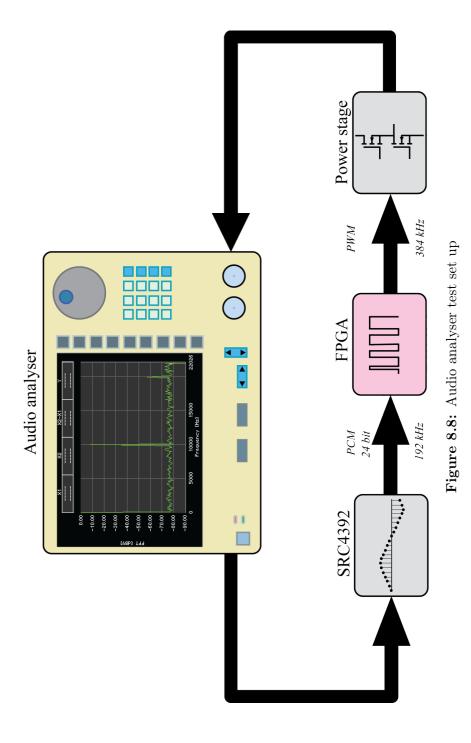

| 8.8  | Audio analyser test set up                                                                                 |       |

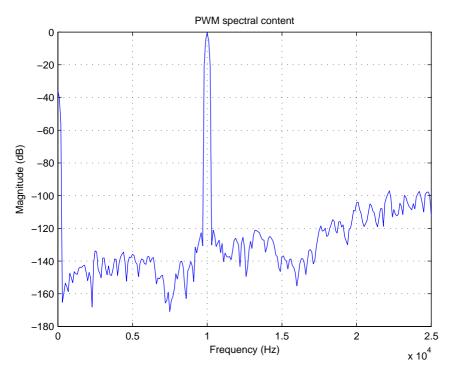

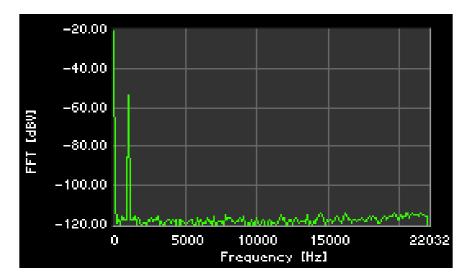

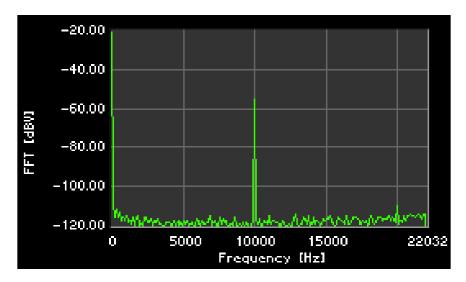

| 8.9  | Spectral content of the PWM signal when a 1 kHz sine wave is used                                          |       |

|      | as the audio input, viewing the audio band                                                                 | . 103 |

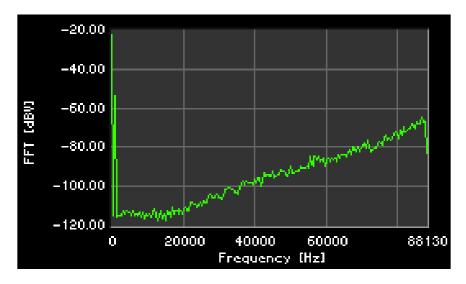

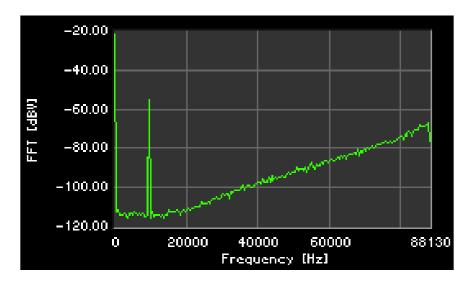

| 8.10 | Spectral content of the PWM signal when a 1 kHz sine wave is used                                          |       |

| 0.20 | as the audio input, viewing a bandwidth of 88 kHz                                                          | 103   |

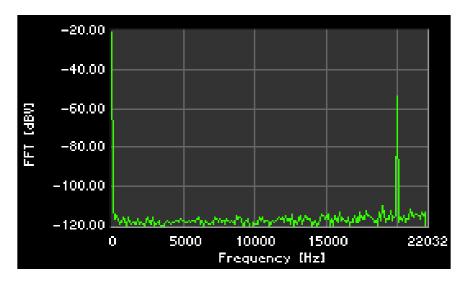

| 8.11 | Spectral content of the PWM signal when a 10 kHz sine wave is                                              | . 100 |

|      | used as the audio input, viewing the audio band                                                            | . 104 |

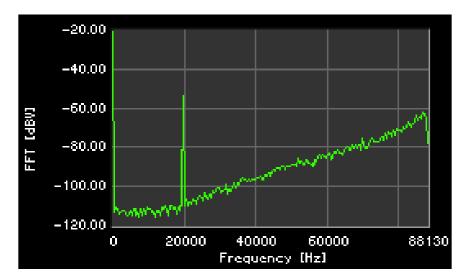

| 8.12 | Spectral content of the PWM signal when a 10 kHz sine wave is                                              | . 101 |

| J.12 | used as the audio input, viewing a bandwidth of 88 kHz                                                     | 104   |

| 8.13 | Spectral content of the PWM signal when a 20 kHz sine wave is                                              | . 101 |

| 3.13 | used as the audio input, viewing the audio band                                                            | . 105 |

|      |                                                                                                            |       |

LIST OF FIGURES xi

| 8.14 | Spectral content of the PWM signal when a 20 kHz sine wave is     |     |

|------|-------------------------------------------------------------------|-----|

|      | used as the audio input, viewing a bandwidth of 88 kHz            | 105 |

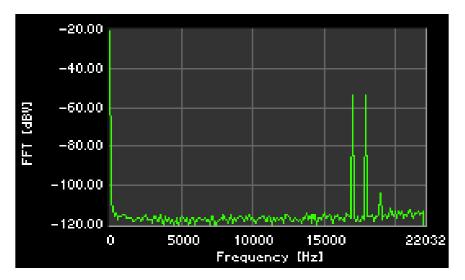

| 8.15 | Spectral content of the PWM signal when a two-tone input at 17    |     |

|      | kHz and 18 kHz is used as the audio input, viewing the audio band | 106 |

# List of Tables

| 1.1 | Required system clock rates for specific PWM resolutions switching at 384 kHz | 3  |

|-----|-------------------------------------------------------------------------------|----|

| 2.1 | A 3 bit 2's complement number representation                                  | 11 |

| 4.1 | Comparison of FIR and IIR filters                                             | 23 |

| 4.2 | FIR filter specifications                                                     | 23 |

| 4.3 | Result of the direct interpolation process                                    | 25 |

| 4.4 | $2^{nd}$ order polynomial divided differences                                 | 36 |

| 4.5 | $2^{nd}$ order polynomial using Neville's algorithm                           | 38 |

| 6.1 | PLL clock generation                                                          | 81 |

| 6.2 | Required FPGA system resources                                                | 91 |

## Nomenclature

#### Abbreviations

ADC Analogue-to-Digital Converter

AES/EBU Audio Engineering Society/European Broadcasting Union

CD Compact Disk

CIC Cascaded Integrator Comb

CIFB Cascade of Integrators with distributed Feedback

CIFF Cascade of Integrators with Feedforward summation

CRFB Cascade of Resonators with distributed Feedback

CRFF Cascade of Resonators with Feedforward summation

DAC Digital-to-Analogue Converter

DAT Digital Audio Tape

DC Direct Current (0 Hz)

DSP Digital Signal Processing

DVD Digital Versatile Disc

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

IIR Infinite Impulse Response

IM Intermodulation

LSB Least Significant Bit

LC Inductor-Capacitor

MAE Minimum Aliasing Error

MIF Memory Initialisation File

MSB Most Significant Bit

NPWM Natural Pulse Width Modulation

NTF Noise Transfer Function

OSR Over Sampling Ratio

PCM Pulse Code Modulation

PLL Phase Lock Loop

PMA Pulse Modulation Amplifier PWM Pulse Width Modulation ROM Read Only Memory NOMENCLATURE xiv

| RMS | Root Mean Square      |

|-----|-----------------------|

| SNR | Signal to Noise Ratio |

S/PDIF Sony/Philips Digital Interconnect Format

SPI Serial Peripheral Interface

SQNR Signal-to-Quantisation Noise Ratio

THD+N Total Harmonic Distortion plus Noise

UPWM Uniform Pulse Width Modulation

VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuit

## Chapter 1

## Introduction

### 1.1 Background

The prevalence of digital audio in our modern world suggests the need for an efficient and exceptional way in which it can be amplified. All audio amplifiers are in some way or another analogue devices, as the final result will always be that of an analogue waveform (Groenenberg et al., 2006). Amplifying audio from a digital source therefore requires digital-to-analogue conversion.

Most amplifier classes are very inefficient. The class-D amplifier however has a theoretical operating efficiency of 100% (Self, 2006). This class has the added advantage of switching between a fully on and fully off state, providing a straightforward means to drive it from digital circuitry. Being able to utilise these benefits offered by a class-D configuration when handling digital audio is therefore an important task.

#### 1.2 Problem statement

The efficiency of a typical analogue amplifier is characteristically less than 40% (Self, 2006). The class-D amplifier is therefore a good substitute for a traditional amplifier when digital audio needs to be amplified due to its switching characteristic and good power efficiency. The class-D amplifier is not a digital system, yet can be better thought of as a Pulse Modulation Amplifier (PMA), where a stream of pulses are increased in amplitude (Nielsen, 1998). The audio signal is modulated onto a carrier at a low power level which is then amplified by the power stage of the class-D amplifier. Its amplified pulse

is subsequently reconstructed by a low-pass filter which then results in an analogue audio waveform.

Pulse Width Modulation (PWM) is a very popular method for modulating the audio signal (Koeslag, 2008). The digital audio would typically be in a Pulse Code Modulation (PCM) format and would need to be converted to PWM. Analogue implementations of PWM are just as successful as digital ones, although using a digital controller for the signal processing allows many additional features to be added to the system's firmware, without adjusting the hardware configuration.

The process of PCM to PWM conversion is inherently nonlinear as well as resulting in low resolution audio due to system clock requirements of the PWM process (Goldberg & Sandler, 1991b).

Compact Disk (CD) audio is encoded with 16-bits at 44.1 kHz while Digital Versatile Disk (DVD) audio is capable of audio encoded with 24-bits at a sampling rate of 192 kHz. These figures quintessentially define what is described as high resolution audio. The problem is how to obtain high resolution PWM which could reproduce such audio data. Very large system clock speeds are required to generate a PWM signal which has 2<sup>16</sup> distinct pulse widths per a pulse period. Needless to say, 2<sup>24</sup> distinct pulses are even more difficult to achieve. Shown in Table 1.1 is a list of system clock rates needed to achieve a desired bit resolution of PWM with a switching rate of 384 kHz. The reason that 384 kHz was chosen as the switching frequency is due to it being a multiple of 48 kHz which is a sample rate used by many professional audio systems, such as Digital Audio Tape (DAT). The value of the switching frequency is selected as being multiple integer times higher than the audio sampling rate so that the switching fundamental and its harmonics would not intrude on the audio band.

| PWM bit resolution | System clock (GHz) |

|--------------------|--------------------|

| 7                  | 0.049152           |

| 8                  | 0.098304           |

| 10                 | 0.393216           |

| 12                 | 1.572864           |

| 16                 | 25.165824          |

| 18                 | 100.663296         |

| 20                 | 402.653184         |

| 24                 | 6442.450944        |

**Table 1.1:** Required system clock rates for specific PWM resolutions switching at 384 kHz

### 1.3 Objectives of the research

The primary objective of this research is to convert PCM to PWM while achieving outstanding audio performance. The various mechanisms which cause the audio signal to deteriorate during the conversion process need to be addressed.

The following research questions became significant:

- Can methods be introduced into the PCM to PWM conversion process which will allow for a high resolution audio output?

- Will these methods effectively linearise the conversion and allow for a realisable system clock?

- Can these methods be implemented in a real-time system on embedded hardware?

Increasing the sampling rate has been shown to improve the linearity (Goldberg & Sandler, 1991a). Sample rate conversion will still not make it possible to achieve high resolution audio, due to the excessively high clock rates required by the pulse width modulator. Clock rates above 200 MHz are considered to be excessively high for this project.

In order to address the problem of a very fast system clock speed, a technique called noise shaping can be employed. It is a process by which the noise floor in the audio band is reduced while still using a low resolution modulator. This would enable a slower clock speed to be used while still obtaining a high resolution audio output.

This thesis will discuss:

- Increasing the linearity of the PCM to PWM conversion process through the use of sample rate conversion,

- reducing the system clock requirements needed to duplicate a high resolution audio signal through the use of noise shaping,

- minimising the system resources required for implementation,

- simulating the various methods presented,

- developing these methods into a control algorithm with VHDL based firmware and

- evaluating the developed firmware on a tangible system.

This thesis will not discuss:

- Design or construction of a class-D power stage and

- analysis of the imperfections introduced by a class-D power stage.

#### 1.4 Structure of the thesis

This thesis is divided into three parts. Firstly an overview of digital signal processing and pulse width modulation is presented. The primary focus of this research is then exhibited with chapters on interpolation and noise shaping. The final part of the thesis is the implementation of the firmware and the results obtained.

Chapter 2 introduces digital signal processing and its use in the modern world. Basic signal theory is highlighted to show the importance of sampling in a digital system and the effect it has on performance. The topic of digital signal processing hardware is broached and popular manufacturers are mentioned.

Chapter 3 concerns pulse width modulation and explains its operation. The difference between generating a pulse width modulated signal in the digital and analogue domains is explained. The harmonic distortion of both methods is presented.

Chapter 4 describes the process of interpolation which is used for sample rate conversion. This forms a significant part of the research. Interpolation helps to linearise the PCM to PWM process. It also increases the bandwidth, which is important for when noise shaping is utilised. Various methods are presented with their advantages and disadvantages discussed.

Chapter 5 introduces noise shaping which is the key to obtaining a high resolution audio output while using a low resolution modulator. Two distinct methods are introduced with an emphasis placed on the second, which is the use of a digital loop filter. Through the use of simulations, this technique is shown to significantly reduce the noise floor in the audio band.

Chapter 6 takes the methodology presented in the previous chapters and describes the formulation of the firmware for an embedded system. The various sections are divided into subsystem blocks.

Chapter 7 discusses problems which were discovered when moving from a simulated system to a physical implementation, and how it led to a redesign of certain subsystems.

Chapter 8 presents the results of the project. Comparisons between Matlab<sup>®</sup> and VHDL simulations are made. The test set up of the embedded real-time system is shown and its results are discussed.

Chapter 9 concludes the thesis by giving an outline of what was discussed and achieved. The possibilities for future research are also mentioned.

# Chapter 2

# Digital signal processing

This chapter introduces elementary digital signal processing (DSP) theory and presents an overview of its applications. Examples are used to illustrate its usefulness in modern electronic engineering.

## 2.1 DSP applications

The application of DSP systems in contemporary life has become invaluable. Without the ability to manipulate and transfer data in a precise and functional manner, many modern marvels would cease to exist. Tan (2008:pg. 11) mentioned just a few of the many applications which are possible with DSP systems, they include:

- Voice recognition,

- speech synthesis systems,

- image and video editing systems,

- digital electrocardiography analysers,

- digital cameras,

- digital recording,

- cellular telephones and

- wireless networks.

DSP provides engineers and scientists with many powerful tools which can be used to visualise and analyse their designs. Applications of DSP are increasing in many areas where analogue electronics are being replaced by a more effective digital counterpart.

### 2.2 Signal sampling and quantisation

It is not possible to digitise all points along a continuous time signal as it contains an infinite number of points. Digital processing hardware could not possibly store an infinite amount of data. Sampling solves this problem by taking samples at discrete time intervals.

The process of transforming an analogue signal into a digital sequence is known as analogue-to-digital conversion. While digital-to-analogue conversion is the reverse process. The end result of this research project is to essentially develop a high powered Digital-to-Analogue Converter (DAC).

#### 2.2.1 Nyquist-Shannon sampling theorem

For a DSP system using uniform sampling, an analogue signal can be perfectly recovered as long as the sampling rate is at least greater than twice the bandwidth of the analogue signal to be sampled (Shannon, 1949). The Nyquist frequency is referred to as  $f_{max}$ , and the minimum sampling frequency  $f_s$ , is called the Nyquist rate.

For a given sampling interval T, which is the time between two sample points, the sampling rate is given by

$$f_s = \frac{1}{T}$$

samples per second (Hz). (2.2.1)

In order to satisfy the criteria of the sampling theorem

$$f_s - f_{max} > f_{max}. (2.2.2)$$

Solving equation (2.2.2) gives

$$f_s > 2f_{max}. (2.2.3)$$

As an example, sampling an audio signal which possesses frequencies up to 20 kHz,  $f_s$  would need to be at least 40 kHz (Tan, 2008). If the Nyquist criteria have been adhered to, then the sampled signal could be reconstructed to its original band limited continuous time form (Stranneby & Walker, 2004).

#### 2.2.2 Aliasing

When sampling a signal which contains frequencies higher than  $f_{max}$ , aliasing occurs. The samples will represent information incorrectly from what is actually present in the original. Once aliasing occurs, it is impossible to reconstruct the original data from the sampled data (Proakis & Manolakis, 1996:pg. 27).

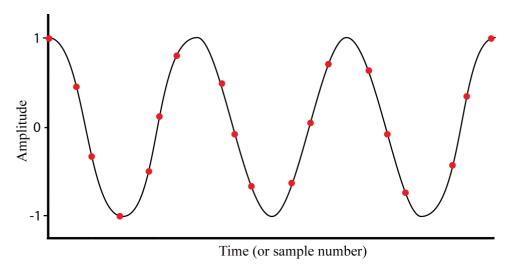

**Figure 2.1:** Correct sampling which will not result in aliasing adapted from Tan (2008)

Figure 2.1 illustrates correct sampling, while Figure 2.2 does not. The frequency of the sine wave in Figure 2.2 is greater than the Nyquist frequency. This results in aliasing, where the frequency of the sampled signal differs from that of the continuous signal. Aliasing corrupts the data and the original signal cannot be reconstructed from the samples.

In practice, the analogue signal may contain high-frequency noise. In order to satisfy the sampling theorem, a low-pass anti-aliasing filter is applied to limit the input analogue signal, so that all the frequency components are less than  $f_{max}$  (Tan, 2008).

### 2.2.3 Quantisation

A quantiser is a nonlinear system that transforms a continuous input signal x(t) into a discrete sequence x[n] for which each value assumes a finite number

Figure 2.2: Incorrect sampling which leads to aliasing adapted from Tan (2008)

of possible values (Hayes, 1999). This operation is represented by

$$x[n] = Q[x(t)].$$

(2.2.4)

Assigning a numerical value to a signal which is analogue and naturally has an infinite number of values, introduces error. The error being the difference between the rounded sample value and the actual value. With rounding, the quantiser error is

$$e[n] = Q[x(t)] - x(t).$$

(2.2.5)

With each additional bit added to the quantiser, the error decreases. According to Hayes (1999), the Signal-to-Quantisation Noise Ratio (SQNR) increases by approximately 6 dB for each bit added. The resulting SQNR yielded from the available bits follows from the equation

$$SQNR \approx 6 \ dB \times bit \ length.$$

(2.2.6)

### 2.3 Hardware for signal processing

Many devices are currently available. The leading manufacturers of DSP chips include Analog Devices<sup>®</sup>, Motorola<sup>®</sup> and Texas Instruments<sup>®</sup>. Their products are dedicated to signal processing.

An alternative to using a DSP chip is to use a Field Programmable Gate Array (FPGA) device. Their versatility has recently led to them being used for many different applications, including signal processing. The primary manufacturers used today are Actel<sup>®</sup>, Altera<sup>®</sup> and Xilinx<sup>®</sup>.

The execution speed of most DSP algorithms is limited almost completely by the number of multiplications and additions required. Yet the computational performance must be known and have a predictable execution time. For an application where processing is continuous, or real-time, there is no definite start or end. All processing needs to be completed in an allotted time-frame. An example would be a DSP system for a hearing aid. The designer would need to make sure that if the digital signal processor is receiving 20 kilo-samples per second, it will be able to maintain that throughput of information constantly.

#### 2.3.1 Fixed point and floating point formats

The arithmetic performed on digital hardware can be divided up into two separate categories, fixed point and floating point. They refer to the format used to store and manipulate data within the device. In particular, the formats are used to represent a negative number using binary (Antoniou, 2006:pg. 620).

Fixed point processors represent the data using integer arithmetic. Floating point on the other hand, represents a number using a mantissa and an exponent in addition to the integer format.

Tan (2008:pg. 420) states that since the fixed point digital signal processor operates using an integer format, overflow of data may occur. This leads to much more time spent on coding an error free fixed point based system. Floating point processors offer a much wider dynamic range of data, leading to overflows occurring much less frequently. However, the floating point processor contains more hardware to manipulate the arithmetic, hence is more expensive and slower than a fixed point processor in terms of instruction cycles.

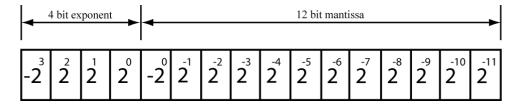

The general format in which a floating point number is given by  $x = M \cdot 2^E$ , where M is the mantissa, or fractional part and E is the exponent. The exponent and mantissa are both signed numbers. Using a word length of 16 bits, a representation is shown in Figure 2.3. 12 bits are assigned to the mantissa and 4 bits to the exponent, where the normalised range is between -1 and 1. The larger the number of bits assigned to the mantissa, the smaller the

interval between values in the normalised range. The larger that the exponent is, the larger the dynamic range becomes.

Figure 2.3: Floating point format adapted from Tan (2008)

It is possible to represent negative values using a fixed point processor using the aforementioned 2's complement concept. The most significant bit (MSB) of the word is used to represent the sign of the integer. Considering a 3 bit 2's complement, all the decimal numbers that can be represented are shown in Table 2.1.

| Decimal number | 2's complement |

|----------------|----------------|

| 3              | 011            |

| 2              | 010            |

| 1              | 001            |

| 0              | 000            |

| -1             | 111            |

| -2             | 110            |

| -3             | 101            |

| -4             | 100            |

Table 2.1: A 3 bit 2's complement number representation

A 16 bit unsigned integer can take on any integer value between 0 and 65535. When 2's complement is employed, the range of integers for a 16 bit word is from -32768 to 32767.

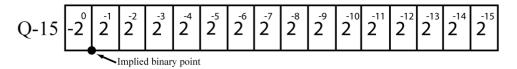

It is also possible to have a fractional binary 2's complement system. Tan (2008) states that the Q-format number representation is the most commonly used fractional implementation in fixed point DSP. Illustrated in Figure 2.4 is a Q-15 representation, Q-15 means that the data is in a signed magnitude form where there are 15 bits for magnitude and one bit for the sign. The number is normalised to the fractional range of -1 to 1. The range is divided into  $2^{16}$

intervals. The most negative number is -1, while the most positive number is  $1-2^{-15}$ .

Figure 2.4: Q-15 (fixed point) format adapted from Tan (2008)

#### 2.4 Conclusion

This chapter introduced three elementary signal theory concepts which were sampling, aliasing and quantisation. These ideas are important to note when digital signal processing is to be employed. The audio information presented to the system will be in the digital domain and therefore digital signal processing becomes pertinent in order to achieve the goals set forth in the first chapter.

Hardware devices which could be used for signal processing were introduced as well as fixed point and floating point number systems.

# Chapter 3

## Pulse width modulation

This chapter describes the concept of Pulse Width Modulation (PWM), presenting a variety of schemes available. Their performance is determined by detailing the harmonic distortion present in the audio band.

Any modulation scheme used for a class-D amplifier aims to create a train of pulses, which when averaged, contains the original reference data (Holmes  $\mathcal{E}$  Lipo, 2003). One of the problems which face designers is that the pulses also contain unwanted harmonics which should be minimised as much as possible.

PWM is a convenient choice when driving a class-D amplifier, due to the switching characteristics of both.

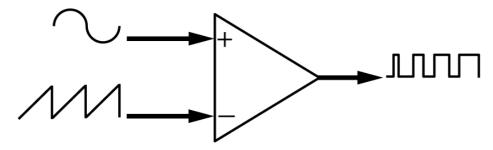

Figure 3.1: Archetype pulse width modulator

## 3.1 Theory of operation

The PWM signal is generated when two waveforms are compared against each other. The one being a low-frequency reference waveform, audio information in this case, and the other a high-frequency carrier waveform. Figure 3.1 is a diagram of this process. The carrier frequency is usually chosen as being at least ten times the highest frequency in the band of interest (Bresch & Padgett, 1999) .

$$f_{sw} \ge 10 \times f_{max} \tag{3.1.1}$$

When the amplitude of the reference is larger than that of the carrier, the output of the comparator is designated a high value, and a low value when the carrier is larger. The carrier can be either a trailing, leading or a double edged waveform. The resulting PWM waveform differs depending on the carrier used and whether natural sampling, shown in Figure 3.1, or uniform sampling, shown in Figure 3.2, is involved.

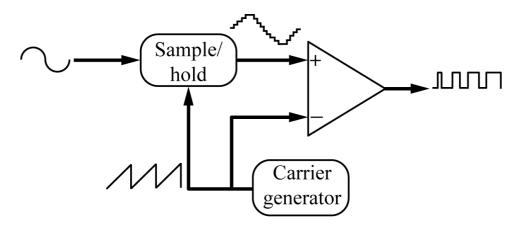

**Figure 3.2:** Uniformly sampled pulse width modulator adapted from Goldberg  $\mathcal{E}$  Sandler (1991a)

## 3.2 Natural and uniform sampling

Natural sampling differs from uniform sampling in that it continuously samples the reference and carrier waveforms. Uniform sampling is employed in discrete time systems and is illustrated in Figure 3.2. The difference which results when using either of these two methods is shown in Figure 3.3. The natural reference is an exaggerated version of what it would be in reality, yet it illustrates that the difference between a continuous and sampled signal can cause an error in the resulting PWM waveform. The error in the time difference between the PWM waveforms results in distortion.

**Figure 3.3:** UPWM and NPWM producing different PWM waveforms adapted from Nielsen (1998) and Jacobs (2006)

#### 3.3 Harmonic distortion

The spectral contents of a PWM signal with a single frequency sinusoidal input have been determined using a two dimensional Fourier series. The contents of a unity-amplitude trailing edge NPWM for modulation by  $M \cos \omega_v t$  into sinusoidal parts yields (Bresch & Padgett, 1999):

$$F(t) = k + \frac{M}{2}\cos\omega_v t + \sum_{m=1}^{\infty} \frac{\sin m\omega_c t}{m\pi}$$

$$-\sum_{m=1}^{\infty} \frac{J_0(m\pi M)}{m\pi} \sin(m\omega_c t - 2m\pi k)$$

$$-\sum_{m=1}^{\infty} \sum_{n=\pm 1}^{n=\pm \infty} \frac{J_n(m\pi M)}{m\pi} \sin(m\omega_c t + n\omega_v t - 2m\pi k - \frac{n\pi}{2}),$$

(3.3.1)

where  $\omega_c$  is the angular fundamental frequency of the PWM carrier,  $\omega_v$  the angular input signal frequency, k the mean amplitude of the unmodulated carrier and  $J_n$  denotes a Bessel function of the first kind. M is the modulation index.

The spectral content includes the input frequency, the sums and differences of the input signal and the carrier and its multiples. There are modulation products of the carrier and input signal which move towards the input signal frequency with decreasing amplitudes. These are referred to as sideband harmonics of the carrier.

The spectral content of a trailing edge UPWM signal yields a rather different result. For the same unity amplitude stimulus as used in Equation 3.3.1 the uniformly sampled PWM spectral content is

$$F(t) = k - \sum_{n=1}^{\infty} \frac{J_n \left(\frac{n\pi M\omega_v}{\omega_c}\right)}{\frac{n\pi\omega_v}{\omega_c}} \sin\left(m\omega_v t - \frac{2n\pi k\omega_v}{\omega_c} - \frac{n\pi}{2}\right)$$

$$+ \sum_{m=1}^{\infty} \frac{1 - J_0(m\pi M)}{m\pi} \sin m\omega_c t$$

$$- \sum_{m=1}^{\infty} \sum_{n=\pm 1}^{n=\pm \infty} \frac{J_n \left[\left(m\omega_c + n\omega_v\right)\right] \frac{\pi M}{\omega_c}}{\left(m\omega_c + n\omega_v\right) \frac{\pi}{\omega_c}} \sin\left(\left(m\omega_c + n\omega_v\right)\left(t - \frac{2\pi k}{\omega_c}\right) - \frac{n\pi}{2}\right).$$

$$(3.3.2)$$

The first sum in Equation 3.3.2 shows that the spectral content includes harmonics of the modulating frequency. The amplitudes of the harmonics increase with an increase of modulation index. It also contains sums and differences of the carrier and modulating signal frequency and multiples of the carrier.

#### 3.4 Conclusion

What is understood is that natural pulse width modulation would be preferred over uniform pulse width modulation. This is due to the harmonic content which is present in the baseband of the uniformly sampled PWM. There is however no way to implement NPWM with a digital controller.

The first solution to this problem is to oversample the audio waveform. When more samples are available for a time period the resulting UPWM will be a closer match to NPWM. Unfortunately the audio data has already been sampled at a rate which is much lower than that which would affect linearity. The only solution is to reconstruct a representation of an analogue version of the waveform and extract new data from it. This is accomplished through the use of interpolation, which is presented in Chapter 4. The usefulness of DSP when used with an audio amplifier becomes more apparent.

## Chapter 4

## Interpolation

#### 4.1 Introduction

The word interpolation has its origins in the Latin word *interpolare*. Which is a combination of *inter*, meaning between and *polare* which means to polish (Meijering, 2002). It is the process of smoothing between the data samples.

Constructing a continuous function becomes a problem when using discrete data which does not contain all of the original information. With so much of the world's data being stored, processed and analysed digitally this is a recurring concern. The easiest and most widely used method for solving this problem is through the use of interpolation. New data is constructed which agrees with the unknown original function (Meijering, 2002).

When a data set is available, interpolation is the method of finding missing data within the confines of the available data. Extrapolation is used when the value of a function outside of the given range is required (Goyal, 2007).

The primary reason for using interpolation in this project is to increase the sample rate of the system. Increasing the sample rate expands the system's frequency bandwidth which then makes it possible to employ certain noise shaping techniques which will be explained in Chapter 5.

This chapter introduces sample rate conversion and its value within the scope of this project. Interpolation is presented as a method of generating new data samples from pre-existing information, which makes sample rate conversion possible. Simulated examples are given to explain the interpolation process.

### 4.2 Sample rate conversion

Increasing or decreasing the sample rate of a digital system is often required in DSP applications. Crochiere & Rabiner (1981) and Tan (2008:pg. 557) gave such examples as antenna systems, communications, radar systems, audio and speech processing as being multi-rate digital systems.

Downsampling or decimation are terms used when referring to the reduction of the sample rate. While upsampling refers to the increase. The focus of this project is to achieve a higher sampling rate, therefore downsampling will be overlooked. If a fractional sample rate change is required, then a combination of both is necessary.

Crochiere & Rabiner (1981) showed that increasing the sample rate  $(T_s)$  by an integer factor of L, would result in a new sampling period of  $T'_s$ , which is

$$\frac{T_s'}{T_s} = \frac{1}{L}. (4.2.1)$$

This would result in a new sample rate being expressed as  $f'_s = Lf_s$ .

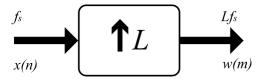

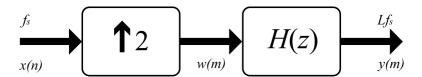

Figure 4.1: Upsampler

Upsampling by a factor L can be achieved by adding L-1 new sample values between each pair of samples. L-1 number of zeros are placed between the data samples which allows for the data to be sampled at a higher rate, as there are now more samples available. Figure 4.1 is a basic block diagram of the process of increasing the sample rate. The input signal x(n) is padded with zeros and then becomes

$$w(m) = \begin{cases} x(m/L), & m = 0, \pm L, \pm 2L, \cdots \\ 0, & otherwise \end{cases}$$

(4.2.2)

The output of the sample rate converter w(n) is described in the z-domain by Crochiere & Rabiner (1981) as being

$$W(z) = \sum_{m=-\infty}^{\infty} w(m)z^{-m}$$

$$= \sum_{m=-\infty}^{\infty} x(m)z^{-mL}$$

$$= X(z^{L}).$$

(4.2.3)

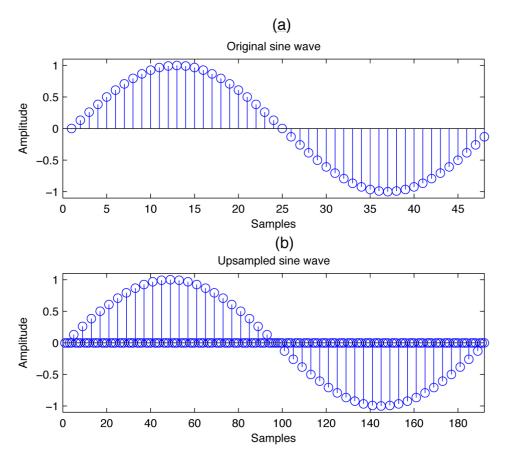

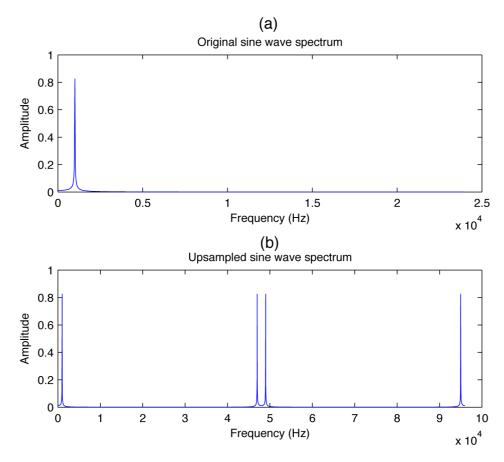

The upper portion, (a), of Figure 4.2 shows a sine wave which was sampled at 48 kHz. The upsampled version where zeros have been place between subsequent samples is shown in the lower portion, (b), of Figure 4.2. By placing three zero valued samples between each original sample, the sample rate is effectively quadrupled.

Figure 4.2: Sine wave before and after upsampling

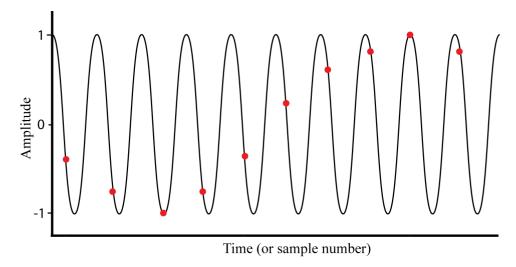

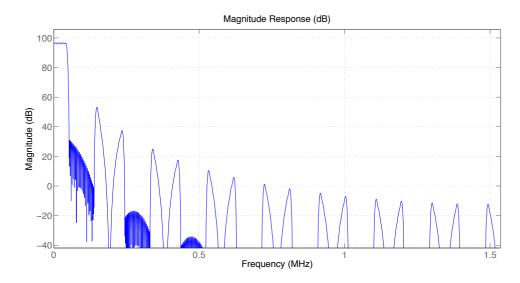

This may seem as though it is the ideal method for achieving any sample rate required. The problem however is evident when viewing the spectral content of the newly upsampled waveform. Figure 4.3 shows the frequency components of Figure 4.2. Aliasing becomes apparent due to the spectral replicas which were originally centred at the sampling frequency,  $f_s$ , and its multiples (Tan, 2008). Due to upsampling, the replicas now sit within the newly increased bandwidth.

Figure 4.3: 1 kHz sine wave spectrum before and after upsampling

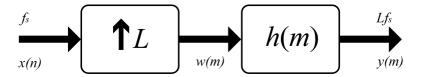

Crochiere & Rabiner (1981) further showed that in order to recover the baseband signal and terminate the unwanted replicas it becomes necessary to filter the signal w(m) with a low-pass filter. Placing the filter in series with the upsampler as shown in Figure 4.4 is necessary. The filter needs to be as

close as it can be to the ideal characteristic of

$$H(e^{j\omega'}) = \begin{cases} G, & |\omega'| \le \frac{2\pi f_s T_s'}{2} = \frac{\pi}{L} \\ 0, & otherwise \end{cases}$$

(4.2.4)

Figure 4.4: Upsampler with low-pass filter

In order for the amplitudes of x(n) and y(m) to match, the gain of the filter G needs to be L in the audio band (Crochiere & Rabiner, 1981). The low-pass filter should have a stop frequency edge of  $f_s/2$  (Tan, 2008).

# 4.3 Finite impulse response interpolation filter

Finite Impulse Response (FIR) as well as Infinite Impulse Response (IIR) filters are the two main categories of filters used for most DSP applications. FIR filters use convolution while IIR filters utilise recursion in their operation. Filters which use convolution outperform those that use recursion, yet they execute at a much slower rate (Antoniou, 2006).

The differences between FIR and IIR filters which were highlighted by Chitode (2009) are detailed in Table 4.1. The FIR filter has an important advantage over the IIR filter, that being a linear phase response in the passband (Jacobs, 2006). It is due to this characteristic that it was the filter type chosen.

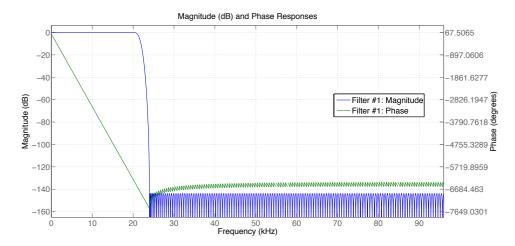

Certain specifications need to be determined when filtering an upsampled signal. The passband and stopband need to be chosen so that they agree with the limits of the audio band. The ripple of the filter needs to be specified for how flat the frequency response is in the audio band. Other important considerations are that of the final sampling frequency and the aliasing attenuation. The filter specifications chosen are shown in Table 4.2. The original sampling frequency was 48 kHz which was then upsampled to 192 kHz.

Matlab<sup>®</sup> was used to design the filter. When the design specifications were placed into Matlab<sup>®</sup> 's Filter Design and Analysis Tool, a filter length of 334

mum coefficients are re-

quired

FIR IIR **Parameter** Do not use feedback Use feedback hence they Recursive/Nonrecursive are recursive Phase Nonlinear phase response Linear phase response Stability Inherently stable Need to be designed for stability Number of multiplica-More Less Less Complexity of imple-More mentation Required memory More Less Order of filter for sim-High Low ilar specifications Design procedure Less complicated Complicated where Used where sharp cutoff Applications Used linear characteristics with miniphase is essential

**Table 4.1:** Comparison of FIR and IIR filters

Table 4.2: FIR filter specifications

| Passband                  | 20  kHz             |

|---------------------------|---------------------|

| Stopband                  | 24  kHz             |

| Passband ripple           | $0.001~\mathrm{dB}$ |

| Stopband attenuation      | 144  dB             |

| Filter sampling frequency | $192~\mathrm{kHz}$  |

points was generated. The magnitude response of the FIR filter is shown in Figure 4.5. It can be clearly seen that the images above 24 kHz have been attenuated.

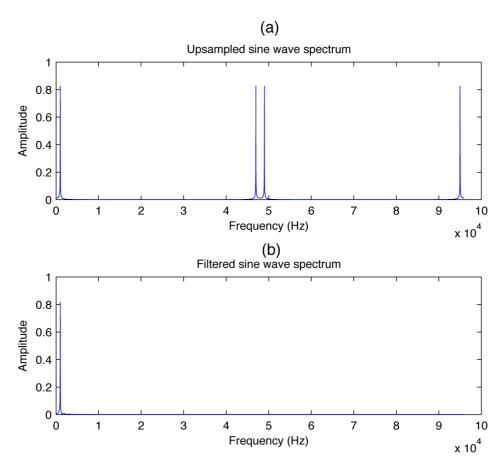

Viewing the phase response of the FIR shown in Figure 4.5 confirms the linear nature which it should have. Note that the phase response is only linear in the passband. The upsampled waveform shown in Figure 4.2 was then applied to the filter. The resulting spectral contents are shown in Figure 4.6.

Figure 4.5: FIR filter magnitude and phase response

Figure 4.6: 1 kHz sine wave spectrum before and after being filtered

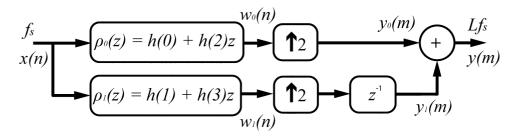

# 4.4 Polyphase interpolation filter

Due to the characteristics of the interpolation process, the polyphase filter structure can be used to efficiently implement the interpolation filter. It uses fewer multiplications and additions to complete the same task as that of a regular FIR described in Section 4.3 (Tan, 2008).

Figure 4.7: Direct interpolation filter

It is an all pass filter with different phase shifts, hence the name polyphase filter. Figure 4.7 shows an interpolation process where L=2. Assuming that the FIR filter has four filter coefficients, shown as

$$H(z) = h(0) + h(1)z^{-1} + h(2)z^{-2} + h(3)z^{-3}.$$

(4.4.1)

The output of the filter would then be

$$y(m) = h(0)w(m) + h(1)w(m-1) + h(2)w(m-2) + h(3)w(m-3). (4.4.2)$$

Tan (2008) showed that with the configuration in Figure 4.7 that eight multiplications and six additions would be required. Table 4.3 shows the results of the direct interpolation of Figure 4.7, where w(m) is the upsampled signal and y(m) is the interpolated output.

Table 4.3: Result of the direct interpolation process

| n     | x(n) | m     | w(m)        | $y(\mathrm{m})$                  |

|-------|------|-------|-------------|----------------------------------|

| n = 0 | x(0) | m = 0 | w(0) = x(0) | y(0) = h(0)x(0)                  |

|       |      | m = 1 | w(1) = 0    | y(1) = h(1)x(0)                  |

| n = 1 | x(1) | m = 2 | w(2) = x(0) | $y(0) = h(0)x(1) \!+\! h(2)x(0)$ |

|       |      | m = 3 | w(3) = 0    | y(0) = h(1)x(1) + h(3)x(0)       |

| n = 2 | x(2) | m = 4 | w(4) = x(0) | y(0) = h(0)x(2) + h(2)x(1)       |

|       |      | m = 5 | w(5) = 0    | y(5) = h(1)x(2) + h(3)x(1)       |

|       |      |       |             |                                  |

The same results shown in Table 4.3 can be calculated using a polyphase structure. The benefit would be that only four multiplications and four additions are required. The polyphase structure for this example is shown in Figure 4.8.

Figure 4.8: Polyphase filter implementation adapted from Tan (2008)

The original FIR filter is split up into L polyphase filters. This characteristic eliminates the need to add zeros between samples (Jacobs, 2006). Once the original filter has been designed containing N coefficients, Tan (2008:pg. 584) showed that the coefficients for the sub filters can be determined according to

$$\rho_k(n) = h(k+nL) \text{ for } k = 0, 1, ..., L-1 \text{ and } n = 0, 1, ..., \frac{N}{L} - 1.$$

(4.4.3)

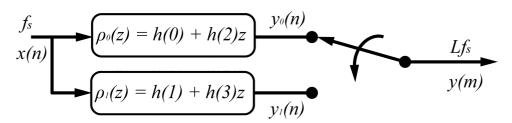

The computational cost can be reduced by a factor of L when compared against the direct interpolation method shown previously. Figure 4.9 shows the commutative model for the polyphase filter. The sample rate increase and delays are replaced by a commutator which alternates between the different branches at a rate of  $Lf_s$ .

**Figure 4.9:** Commutative model for the polyphase interpolation filter adapted from Tan (2008)

This is where the efficiency of the polyphase filter becomes apparent. The filtering is performed at the original sampling rate of  $f_s$  which is much lower

than  $Lf_s$  (Jacobs, 2006). Direct FIR interpolation requires the sample rate of the filtering to be at the higher sample rate of  $Lf_s$ .

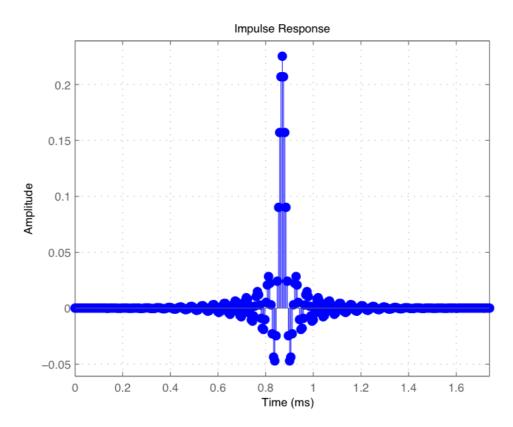

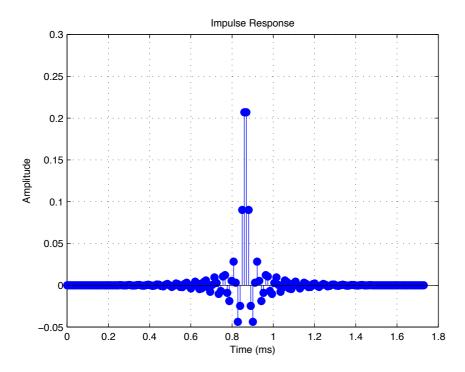

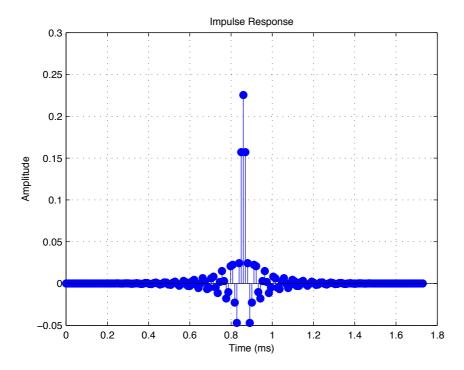

The impulse response of the original FIR filter is shown in Figure 4.10 while the impulse responses of the two polyphase filters is shown in Figure 4.11 and Figure 4.12.

Figure 4.10: Impulse response of the original FIR filter

Figure 4.11: Impulse response of the first polyphase filter

Figure 4.12: Impulse response of the second polyphase filter

# 4.5 Cascaded integrator comb filter

Hogenauer (1981) developed the Cascaded Integrator Comb (CIC) filter for multi-rate processing. It is a digital linear phase FIR filter specifically aimed at decimation and interpolation as it has a low-pass characteristic. The primary benefits of using this filter type are:

- No multipliers are required,

- no filter coefficients need to be stored in memory,

- the structure is very consistent and made up of only two building blocks,

- no complicated timing is required and

- the same filter can be used for many different sample rate change ratios with minimal adjustments required.

There are however limiting factors when using this filter type, they include:

- Register word lengths can become large for large sample rate changes. The register word length increases exponentially for each additional stage added to the filter.

- The filter's characteristics and frequency response is limited due to being influenced by only three parameters, the sample rate change ratio, L, the differential delay, M, and the number of integrator-comb pairs, N.

The advantages and disadvantages make this filter ideal for systems requiring large rate changes while utilising minimal resources.

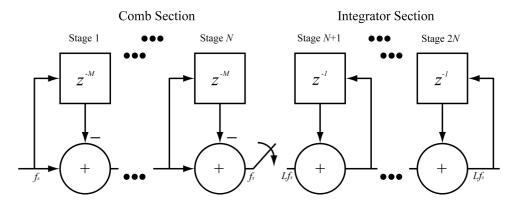

The filter consists of integrator-comb pairs which produce a consistent FIR. When interpolation is required, the integrators operate at the new desired sample rate, while the comb section operates at the slower original sample rate. This is another benefit of the filter as half the processing is conducted using a slower clock. The number of integrator-comb pairs is chosen in accordance with the requirements for image attenuation.

The interpolating CIC filter structure is shown in Figure 4.13.

Figure 4.13: CIC filter block diagram adapted from Hogenauer (1981)

The transfer function for each integrator which operates at a sampling rate of  $Lf_s$ , where L is the oversampling ratio, is

$$H_I(z) = \frac{1}{1 - z^{-1}}. (4.5.1)$$

The comb section operates at the original sampling rate of  $f_s$ . The differential delay, M, is a design parameter used to control the frequency response of the filter. The transfer function for each comb section is

$$H_C(z) = 1 - z^{-LM}.$$

(4.5.2)

The rate change occurs by placing L-1 zero value samples between the original data samples coming out of the comb section. Combining Equations 4.5.1 and 4.5.2 yields a transfer function for the CIC filter of

$$H(z) = H_I^N(z)H_C^N(z) = \frac{(1 - z^{-LM})^N}{(1 - z^{-1})^N} = \left[\sum_{k=0}^{LM-1} z^{-k}\right]^N.$$

(4.5.3)

When designing a CIC interpolator, attention needs to be paid to the bit growth of the filter sections. The introduction of a small error into the integrator stages, resulting from rounding, would cause the error difference to increase until the filter becomes unstable. Therefore the maximum word length for each stage needs to be known and accommodated for. Both Frerking (1994) and Hogenauer (1981) mentioned the importance of not truncating the word lengths within the integrator stages.

The maximum word length increase up to the  $j^{th}$  stage can be shown to be

$$G_{j} = \begin{cases} 2^{j} & j = 1, 2, \dots, N \\ \frac{2^{2N-j}(LM)^{j-N}}{L} & j = N+1, \dots, 2N \end{cases}$$

(4.5.4)

The minimum word length required, based on the growth  $G_j$ , where  $B_{in}$  is the input word length, is

$$W_{i} = B_{in} + log_{2}G_{i}. (4.5.5)$$

Truncation can only be employed after the last integrator stage. This becomes the only error introduced. The number of LSBs which can be discarded, where  $B_{out}$  is the output word length, is

$$B_T = W_{2N} - B_{out}. (4.5.6)$$

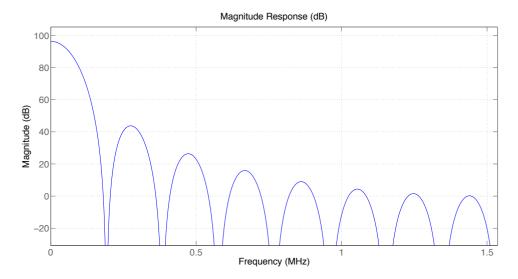

Matlab<sup>®</sup> provides a filter design tool to help with creating a CIC filter. Even though the basic building blocks will always remain the same, the amount of stages required is easily determined when using the filter design tool. As an example, the following characteristics can be specified and designed in Matlab<sup>®</sup>:

- Differential delay = 1,

- interpolation ratio = 16,

- pass band frequency = 22 kHz,

- desired sampling rate = 3.072 MHz and

- the aliasing attenuation = 60 dB.

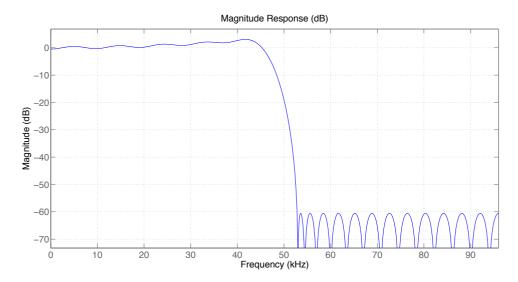

The resulting filter has four sections with a magnitude response shown in Figure 4.14. This filter will upsample a 192 kHz waveform to 3.072 MHz using only a minimal amount of resources. It is evident from Figure 4.14 that truncation of the output is necessary as the gain of the filter is very large.

Figure 4.14: CIC filter magnitude response

### 4.5.1 CIC compensation filter

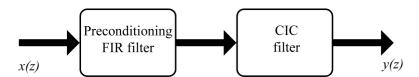

An unfortunate characteristic of the CIC filter is its non-flat frequency response. There is a way to obtain the benefits gained from using a CIC filter while still maintaining a good frequency response. Cascading a conventional FIR filter in conjunction with the CIC filter allows for the frequency response to be modified to compensate for imperfections. Figure 4.15 shows the configuration which would achieve this.

Figure 4.15: CIC compensation filter block diagram

Matlab<sup>®</sup> can again be used to design the compensation filter as it has specific functionality for this purpose. By entering the number of stages which the CIC filter requires, the filter design tool will generate an FIR filter to help counteract the habitual CIC shape. Figure 4.16 shows the magnitude response of such a filter.

When both filters are cascaded, as shown in Figure 4.15, the magnitude response becomes that shown in Figure 4.17. The cutoff is now much sharper.

Figure 4.16: CIC compensator filter magnitude response

Figure 4.17: Magnitude response of a CIC filter cascaded with a CIC compensator

Depending on the FIR filter used, a better response could be achieved. If resources are vital, which would be the reason for not using a FIR filter in the first place, a half-band FIR filter could be employed. Half-band filters have every second coefficient reduced to zero, making them computationally inexpensive (Lutovac *et al.*, 2001). The performance of a normal FIR filter is achieved while only paying the computational price of half the multiplications.

Lutovac et al. (2001) further mentioned that a limiting factor when using the half-band filter is that the frequency symmetry condition must be met, which is

$$f_{stopband} = \frac{1}{2} - f_{passband}. (4.5.7)$$

This means that the design boundaries are constrained. The transition region is centred at a quarter of the sampling rate.

# 4.6 Polynomial interpolation

This method of interpolation involves constructing a curve through a specific set of data points. Trefethen (2000), Cohen *et al.* (2001), Stetter (2004), Kiusalaas (2005), Goyal (2007), Lyons (2007) and Butt (2008) have presented polynomial interpolation using many different methods.

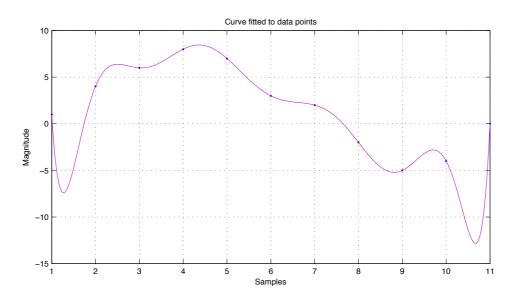

Constructing a polynomial of degree n-1 which will pass through n distinct data points is always possible (Kiusalaas, 2005). The concept is that the polynomial would follow the natural path that a continuous signal would follow through the data points.

If constructed correctly, any new data point could be found along the polynomial, thereby generating as much new data as is required. This idea is illustrated in Figure 4.18 where a fifth order polynomial is constructed passing through six data points. The methods for approximating the polynomial and generating new data from it vary. The Lagrange method as well as Neville's formula and Newton's interpolation formula are presented in the following sections.

## 4.6.1 Lagrange interpolation

Given the data points  $x_0, x_1...x_n$  where  $f(x_0), f(x_1)...f(x_n)$  are their corresponding magnitudes, the point located at x can be found through an uncomplicated calculation. Goyal (2007) derived Lagrange's interpolation formula to

Figure 4.18: Curve constructed from discrete data points

be

$$f(x) = \frac{(x - x_1)(x - x_2)...(x - x_n)}{(x_0 - x_1)(x_0 - x_2)...(x_0 - x_n)} f(x_0)$$

$$+ \frac{(x - x_0)(x - x_2)...(x - x_n)}{(x_1 - x_0)(x_1 - x_2)} f(x_1)$$

$$+ ... + \frac{(x - x_0)(x - x_1)...(x - x_{n-1})}{(x_n - x_0)(x_n - x_1)...(x_n - x_{n-1})} f(x_n).$$

(4.6.1)

Lyons (2007) showed that the Lagrange formula could also be represented as

$$f(x) = \sum_{i=0}^{n} f(x_i) \prod_{j=0, j \neq i}^{n} \frac{x - x_j}{x_i - x_j}.$$

(4.6.2)

Lagrange's method is simple in theory, yet it is not an efficient algorithm. For each new data point required, a substantial amount of calculation is required. When implemented on embedded hardware the amount of multipliers and time required would be unacceptable. This method is accurate and would be a good choice if only one new data sample was needed.

### 4.6.2 Newton's interpolation formula

This method of interpolation gains efficiency by calculating the polynomial coefficients and new data values in two separate calculation steps. This means that once the coefficients have been calculated, there can be any number of new data points generated without recalculating the coefficients.

In order to calculate the coefficients for the polynomial, a divided differences method can be employed. Determining the values of a divided differences table can be completed by using the formula

$$\Delta^{n} f_{i} = f_{i+n} - n f_{i+n-1} + \frac{n(n-1)}{2!} f_{i+n-2} - \frac{n(n-1)(n-2)}{3!} f_{i+n-3}$$

$$+ \dots + (-1)^{n} f_{i}.$$

$$(4.6.3)$$

Creating a divided differences table helps to calculate and collate the coefficients. Table 4.4 shows how to set out a divided differences table when calculating a  $2^{nd}$  order polynomial.

**Table 4.4:**  $2^{nd}$  order polynomial divided differences

| $\boldsymbol{x}$ | f(x)  | $\Delta f(x)$                 | $\Delta^2 f(x)$                             |

|------------------|-------|-------------------------------|---------------------------------------------|

| $x_0$            | $y_0$ |                               |                                             |

|                  |       | $\frac{y_1 - y_0}{x_1 - x_0}$ |                                             |

| $x_1$            | $y_1$ |                               | $\frac{\Delta f_0 - \Delta f_1}{x_2 - x_0}$ |

|                  |       | $\frac{y_2 - y_1}{x_2 - x_1}$ |                                             |

| $x_2$            | $y_2$ |                               |                                             |

From Table 4.4 the coefficients are taken as the top value of each row, except the first row which contains the data position. Therefore the coefficients for a  $2^{nd}$  order polynomial would become

$$a_0 = y_0$$

$$a_1 = \frac{y_1 - y_0}{x_1 - x_0}$$

$$a_3 = \frac{\Delta f_0 - \Delta f_1}{x_0 - x_0}$$

Once the coefficients have been calculated then any new data point can be generated. When n-data points are used, an n-1 order polynomial is possible. The equation used to determine a desired value at point x is

$$f(x) = a_0 + (x - x_0)a_1 + (x - x_0)(x - x_1)a_2 + \dots + (x - x_0)(x - x_1)\dots(x - x_{n-1})a_n.$$

$$(4.6.4)$$

This equation may appear to be just as computationally expensive as the Lagrange method, yet it is possible to pre-calculate most of the equation offline and store it in a lookup table. If the same amount of new data values at the same points need to be generated each time the coefficients are updated then Equation 4.6.4 can be simplified to

$$f(x) = a_0 + v_1 a_1 + v_2 a_2 + \dots + v_n a_n. \tag{4.6.5}$$

Equation 4.6.5 drastically reduces the amount of multipliers required for each iteration. The values of  $v_1...v_n$  would be the information stored in a lookup table.

#### 4.6.3 Neville's formula

Neville's formula is based on a similar principle to Newton's interpolation formula (Kiusalaas, 2005). It forms a triangular shaped set of results, appearing similar to that of a divided differences table. The formula is recursive and each iteration fits a polynomial of a degree higher than the previous iteration. The number of iterations relates to the order of the polynomial required.

If  $P_k[x_j, x_{j+1}, ..., x_{j+k}]$  represents a polynomial of degree k that passes through k+1 data points. Then the general recursive formula as presented by Kiusalaas (2005) is

$$P_{k}[x_{i}, x_{i+1}, ..., x_{i+k}] = \frac{(x - x_{i+k})P_{k-1}[x_{i}, x_{i+1}, ..., x_{i+k-1}] + (x_{i} - x)P_{k-1}[x_{i+1}, x_{i+2}, ..., x_{i+k}]}{x_{i} - x_{i+k}}.$$

$$(4.6.6)$$

When searching for the value of x, the calculations can be conducted using a table as shown in Table 4.5.