## HARDWARE IN THE LOOP SIMULATION AND TESTING OF VOLTS PER HERTZ PROTECTION SCHEME FOR A GENERATOR OVEREXCITATION SYSTEM

Bу

KHANGWELO LOYD RATHOGWA

Thesis submitted in fulfilment of the requirements for the degree Master of Engineering: Electrical Engineering

In the Faculty of Engineering and the built Environment

At the Cape Peninsula University of Technology

Supervisor : Dr. S Krishnamurthy

Bellville December 2022

#### **CPUT** copyright information

The thesis/dissertation may not be published either in part (in scholarly, scientific or technical journals), or as a whole (as a monograph), unless permission has been obtained from the University

### DECLARATION

I, Khangwelo Loyd Rathogwa, certify that the information contained in this thesis or dissertation is entirely my own original work and has never before been submitted for academic review in order to obtain a degree. The views expressed here are also solely mine and do not necessarily reflect those of Cape Peninsula University of Technology.

Allet

Signed

.

09 December 2022 Date

#### ABSTRACT

A power plant's large generators are essential components for ensuring the steady production and delivery of electric power for a variety of purposes. A power system's stability is greatly impacted by the generator protection system. It has recently become necessary to think about upgrading the existing protective devices due to a rise in power demand and their aging. The over-excitation, overvoltage, and undervoltage circumstances that affect generators as well as their protection mechanisms were the subject of this study. The analyses of the various method used for generator protection is conducted in this research as part of the literature review. The research developed a logic design and algorithm for volts per hertz protection strategy for overexcited generators. The logic design of over and under-voltage conditions is also developed. The implementation of the current differential and overcurrent protection schemes for generator using DIgSILENT power factory simulation environment is performed and the simulation results are studied for both normal and abnormal conditions for both current differential and overcurrent protection schemes. The lab scale test bench to test volts per hertz, a backup overcurrent, over and under voltage protection schemes for a generator is implemented using SEL 700G IED and simulation results are analysed and presented. The hardware in the loop test-bed is implemented to test analyse the volts per hertz, simple back up overcurrent, and overvoltage and under voltage protection schemes. The HIL test bed was implemented using real time digital simulator and SEL 700G IED. The Hardware-inthe-Loop simulation results for over excitation conditions, overcurrent fault events, over and under voltage conditions of a generator is presented.

**Keywords:** Generator Over-excitation system, Volts per hertz, overvoltage, under voltage, overcurrent, and Hardware-in-the-Loop simulations.

### ACKNOWLEDGEMENTS

### I wish to thank:

- My supervisor, **Dr. Senthil Krishnamurthy** for his excellent mentorship, advice, assistance, availability, patience and support.

- The CPUT Library management and staff for their support and willing to provide me with the information needed for this study.

- All My CSAEMS colleagues for their support.

## DEDICATION

This thesis is dedicated to my father Nnditsheni Justice Rathogwa and my entire family. Further dedication goes to my fiancée Rolivhuwa Masiagwala.

# TABLE OF CONTENTS

## Contents

| DECLARATION                                                                        | ii     |

|------------------------------------------------------------------------------------|--------|

| ABSTRACT                                                                           | iii    |

| ACKNOWLEDGEMENTS                                                                   | iv     |

| DEDICATION                                                                         | v      |

| TABLE OF CONTENTS                                                                  | vi     |

| LIST OF FIGURES                                                                    | X      |

| LIST OF TABLES                                                                     | xii    |

| GLOSSERY                                                                           | xiv    |

| NOMENCLATURE                                                                       | . xvii |

| CHAPTER ONE                                                                        | 1      |

| INTRODUCTION                                                                       | 1      |

| 1.1 Introduction                                                                   | 1      |

| 1.2 Awareness of the problem                                                       | 2      |

| 1.3 Problem statement                                                              | 3      |

| 1.4 Research Aim and objectives                                                    | 4      |

| 1.4.1 Aim                                                                          | 4      |

| 1.4.2 Objectives                                                                   | 4      |

| 1.5 Hypothesis                                                                     | 5      |

| 1.6 Motivation of the research project                                             | 5      |

| 1.7 Assumptions                                                                    | 5      |

| 1.8 Research Methodology                                                           | 6      |

| 1.8.1 Literature review                                                            | 6      |

| 1.8.2 Network Data collection                                                      | 6      |

| 1.8.3 Modelling and Simulation                                                     | 6      |

| 1.8.4 Algorithm development                                                        | 6      |

| 1.8.5 Lab scale Test Bench Setup and Hardware-in-the-loop simulation               | 6      |

| 1.9 Thesis chapter breakdown                                                       | 7      |

| 1.9.1 Chapter 1                                                                    | 7      |

| 1.9.2 Chapter 2                                                                    | 7      |

| 1.9.3 Chapter 3                                                                    | 7      |

| 1.9.4 Chapter 4                                                                    | 7      |

| 1.9.5 Chapter 5                                                                    | 7      |

| 1.9.6 Chapter 6                                                                    | 7      |

| 1.9.7 Chapter 7                                                                    | 7      |

| 1.10 Conclusion                                                                    | 8      |

| CHAPTER TWO                                                                        | 9      |

| LITERATURE REVIEW                                                                  | 9      |

| 2.1 Introduction                                                                   | 9      |

| 2.2 Literature review overview                                                     | 10     |

| 2.3 Over excitation condition and volts per hertz protection scheme of a generator | 11     |

| 2.3.1  | Generator over excitation                                                               | . 11 |

|--------|-----------------------------------------------------------------------------------------|------|

| 2.3.2  | Volts per hertz protection scheme                                                       | . 11 |

| 2.4    | Overvoltage conditions of a generator system                                            | . 13 |

| 2.5    | Under voltage conditions of a generator system                                          | . 13 |

| 2.6    | Review overview of volts per hertz, over and under voltage protection schemes           | . 14 |

| 2.7    | The Review of the existing papers on volts per hertz, over and under voltage protection |      |

| scheme |                                                                                         |      |

| 2.8    | Hardware in the loop simulation using RTDS and IEDs                                     |      |

| 2.9    | Review overview simulation using HIL Simulation for a generator system                  |      |

| 2.10   | The Review of the existing papers on HIL, RTDS and IEDs for a generator system          |      |

| 2.11   | Conclusion                                                                              |      |

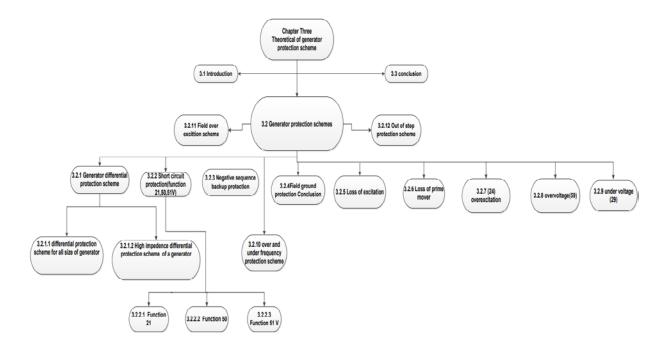

|        | R THREE                                                                                 |      |

| THEORE | CAL ASPECT OF GENERATOR PROTECTION SCHEME                                               | . 27 |

| 3.1    | Introduction                                                                            |      |

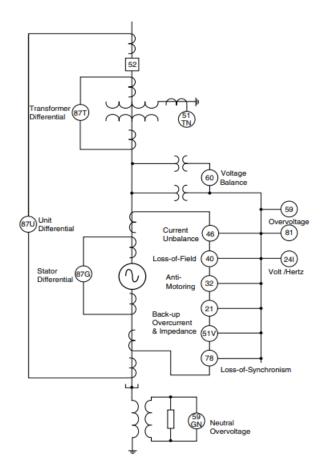

| 3.2    | Generator Protection schemes                                                            | . 28 |

| 3.2.1  | Generator differential protection scheme (87)                                           | . 28 |

| 3.2.2  | Short-Circuit Protection (Functions 21, 50, 51V,)                                       | . 30 |

| 3.2.3  | Negative-Sequence Current Backup Protection                                             | . 31 |

| 3.2.4  | Field-Ground Protection (64)                                                            | . 32 |

| 3.2.5  | Loss of excitation (40)                                                                 | . 32 |

| 3.2.6  | Loss of prime mover (32)                                                                | . 33 |

| 3.2.7  | (24) Over-excitation Protection                                                         | . 33 |

| 3.2.8  | Over-voltage (59)                                                                       | . 35 |

| 3.2.9  | Under-voltage (27)                                                                      | . 36 |

| 3.2.1  | 0 Over- and Under- Frequency Protection scheme                                          | . 36 |

| 3.2.1  | 1 Field Over-excitation protection scheme                                               | . 37 |

| 3.2.1  | 2 Out of step protection scheme                                                         | . 37 |

| 3.3    | Conclusion                                                                              | . 37 |

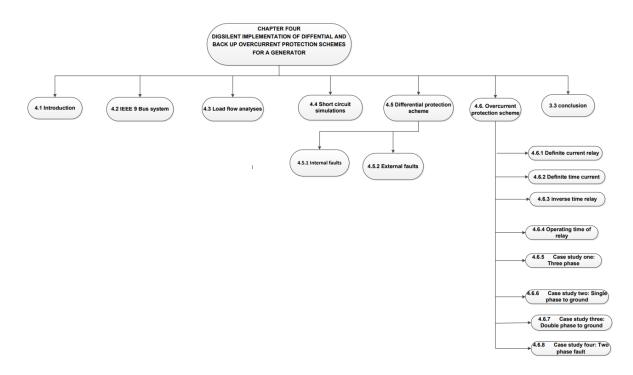

| CHAPTE | R FOUR                                                                                  | . 38 |

|        | NT IMPLEMENTATION OF DIFFENTIAL AND BACK UP OVERCURRENT PROTECTION                      |      |

| SCHEME | S FOR A GENERATOR                                                                       |      |

| 4.1    | Introduction                                                                            |      |

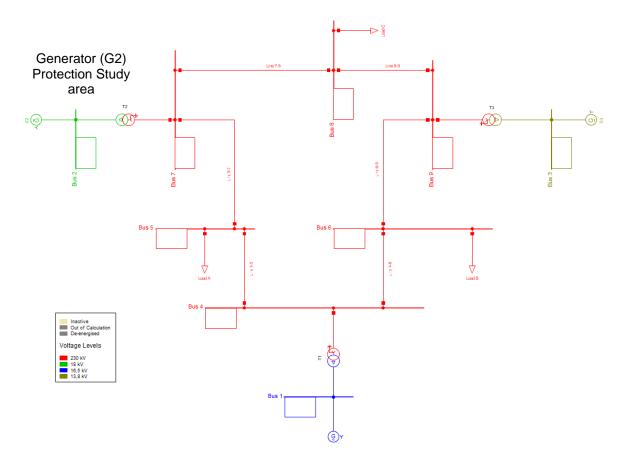

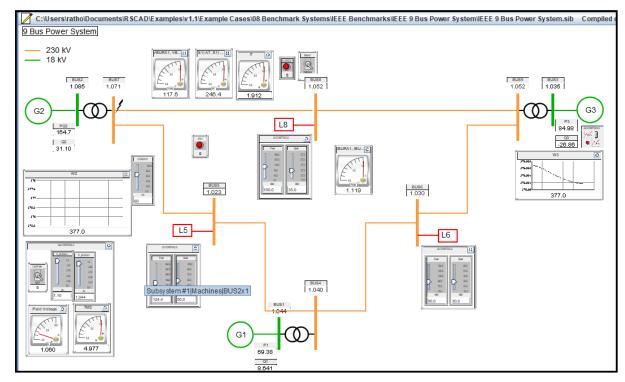

| 4.2    | IEEE 9 Bus system                                                                       | . 40 |

| 4.3    | Load flow analysis                                                                      | . 41 |

| 4.4    | Short Circuit Simulation                                                                | . 44 |

| 4.5    | Differential protection functions of a power generator                                  | . 46 |

| 4.5.1  | Internal faults                                                                         | . 49 |

| 4.5.2  | External faults                                                                         | . 58 |

| 4.6    | Overcurrent protection functions of a power generator                                   | . 66 |

| 4.6.1  | Definite Current relays                                                                 | . 66 |

| 4.6.2  | Definite Time relays                                                                    | . 66 |

| 4.6.3  | Inverse Time relays                                                                     | . 66 |

| 4.6.4  | Operating time of relay defined by IEC 60255 and IEEE C37.112                           | . 67 |

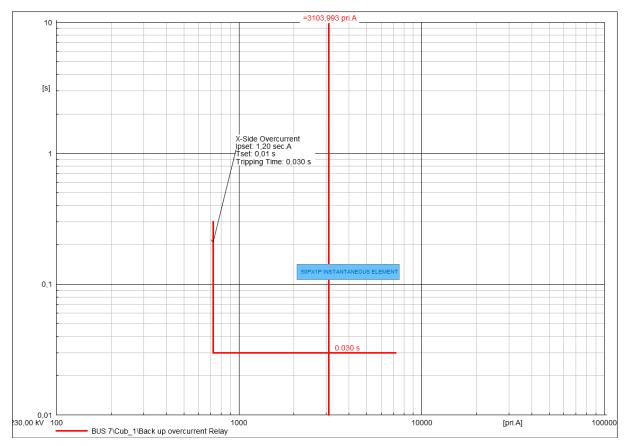

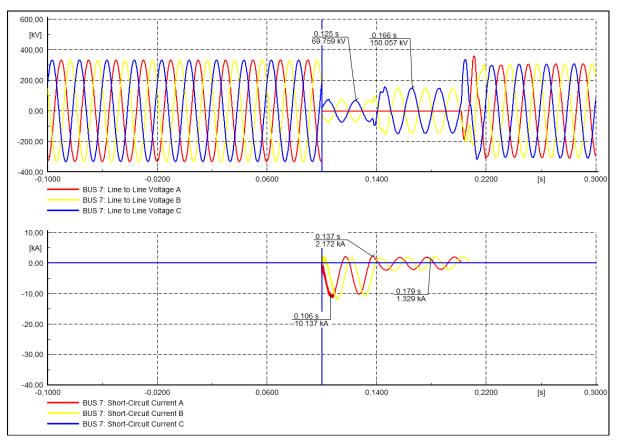

| 4.6.5  | Case study one: Three phase fault at bus 7                                              | . 68 |

|                                                                                                                                                                                          | 6 Case study two: Single phase to ground fault at bus 7                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

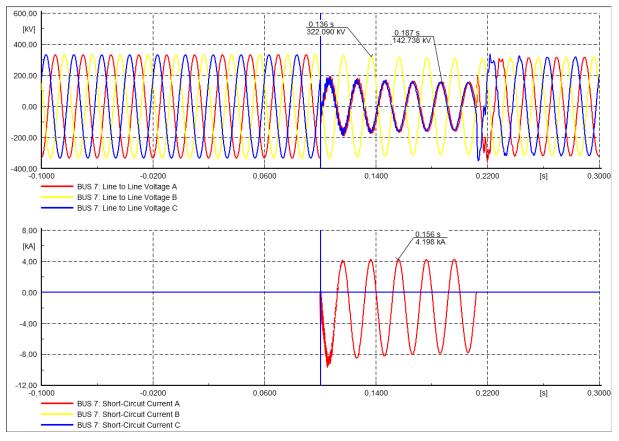

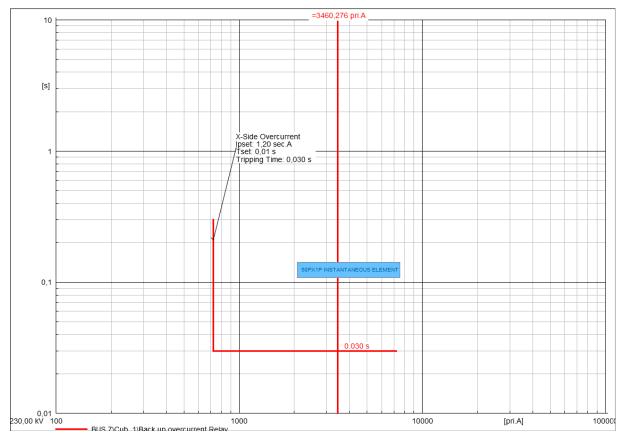

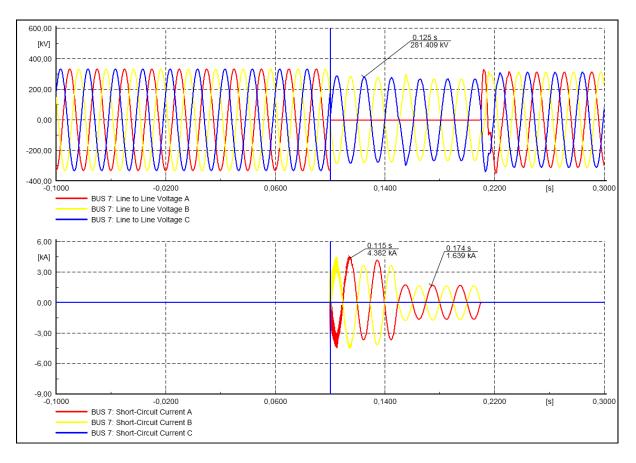

| 4.6.                                                                                                                                                                                     | 7 Case study three: Double phase to ground fault at bus 7                                                                                                                                                                                                                                                                                                                                                                                                                                               | 72                                                                                                                 |

| 4.6.8                                                                                                                                                                                    | 8 Case study four: Two phase fault at bus 7                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                                                                                                 |

| 4.7                                                                                                                                                                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                                                 |

| CHAPTE                                                                                                                                                                                   | R FIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77                                                                                                                 |

| OVERCU                                                                                                                                                                                   | ENTATION OF THE LAB SCALE TEST BENCH TO TEST VOLTS PER HERTZ, A BACK<br>JRRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEMES FOR A GENERAT                                                                                                                                                                                                                                                                                                                                                                 | OR                                                                                                                 |

|                                                                                                                                                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                    |

| 5.2                                                                                                                                                                                      | SEL 700G Volts per Hertz (24) protection setting on numerical relay                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    |

| 5.2. <sup>-</sup>                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.2.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.2.3                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.2.4                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.3.                                                                                                                                                                                     | SEL 700G Overcurrent back up protection setting for a generator                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.3.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.3.2                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.3.3                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.4.                                                                                                                                                                                     | SEL 700G Overvoltage and under voltage protection setting for a generator                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                    |

| 5.4.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

|                                                                                                                                                                                          | ware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |

| 5.4.2                                                                                                                                                                                    | 2 OMICRON Test Universe configuration setting for Over- and under- voltage rel.<br>112                                                                                                                                                                                                                                                                                                                                                                                                                  | ау                                                                                                                 |

| 5.4.3                                                                                                                                                                                    | 3 SEL 700G Overvoltage protection (59) testing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 115                                                                                                              |

| 5.4.4                                                                                                                                                                                    | 4 SEL 700G under voltage (27) protection testing                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 119                                                                                                              |

| 5.5                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |

| 5.5                                                                                                                                                                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 122                                                                                                              |

|                                                                                                                                                                                          | R SIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    |

| CHAPTE<br>IMPLEM<br>HERTZ,                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 123<br>S                                                                                                         |

| CHAPTE<br>IMPLEM<br>HERTZ,                                                                                                                                                               | R SIX<br>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME                                                                                                                                                                                                                                                                                                                                                           | . 123<br>S<br>. 123                                                                                                |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G                                                                                                                                                    | ER SIX<br>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br>GENERATOR                                                                                                                                                                                                                                                                                                                                             | . 123<br>S<br>. 123<br>. 123                                                                                       |

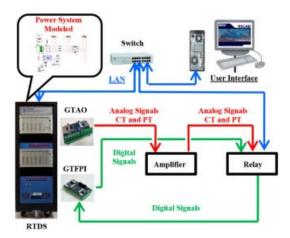

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3                                                                                                                               | R SIX<br>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br>GENERATOR<br>Introduction                                                                                                                                                                                                                                                                                                                              | . 123<br>S<br>. 123<br>. 123<br>. 123                                                                              |

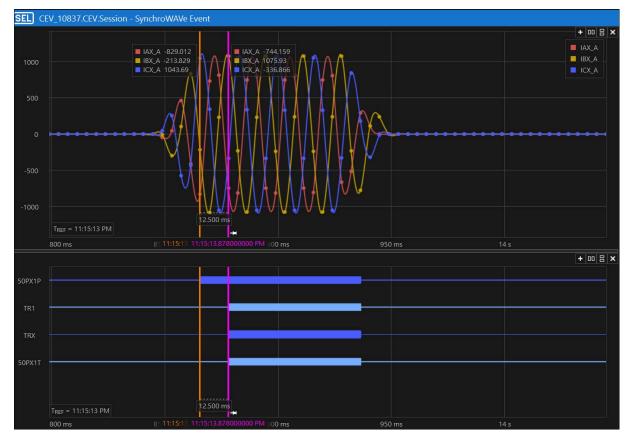

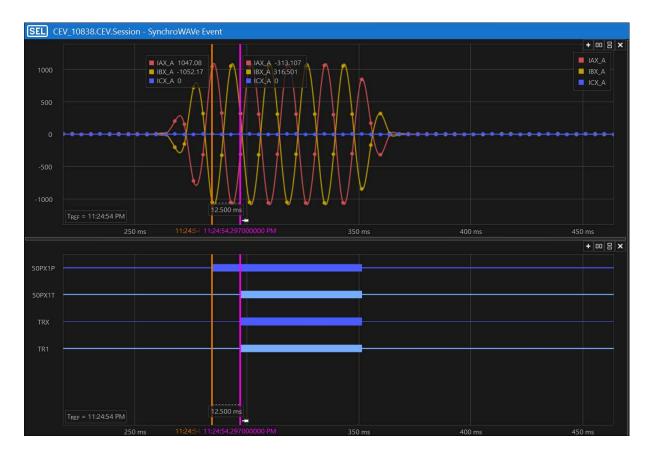

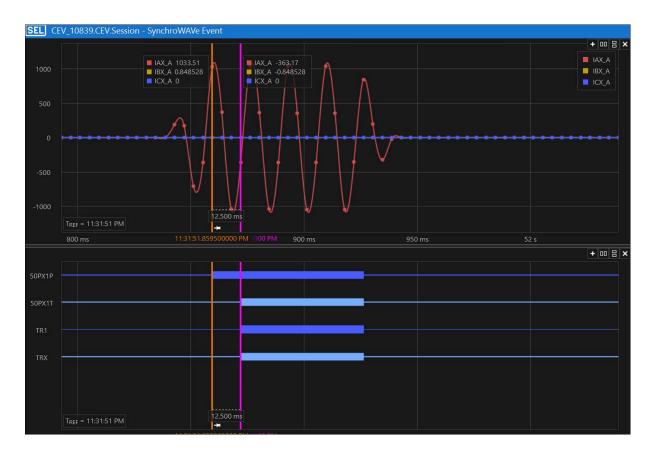

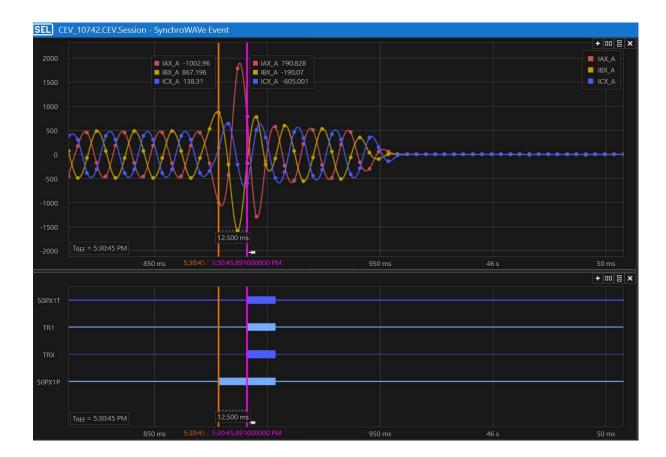

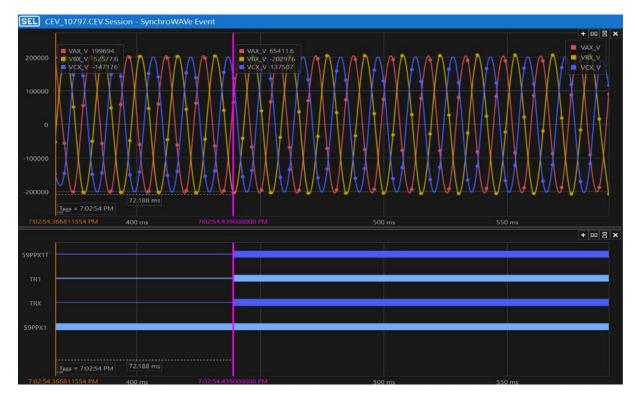

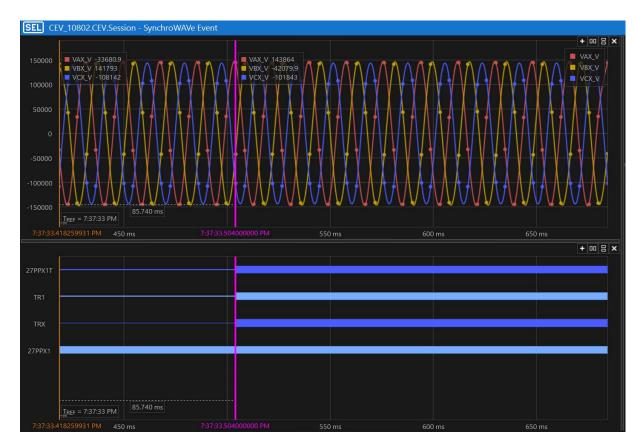

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.                                                                                                              | ER SIX<br>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br>GENERATOR<br>Introduction<br>IEEE 9-Bus system<br>The hardware in the loop simulation test-bed implementation for a generator protection<br>nes                                                                                                                                                                                                       | . 123<br>S<br>. 123<br>. 123<br>. 123<br>. 124<br>. 125                                                            |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.                                                                                                              | ER SIX<br>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br>SENERATOR<br>Introduction<br>IEEE 9-Bus system<br>The hardware in the loop simulation test-bed implementation for a generator protection<br>res<br>1 The implementation of hardware in the loop test-bed for generator volts per hertz<br>ection scheme using SEL 700G IED.                                                                           | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126                                                            |

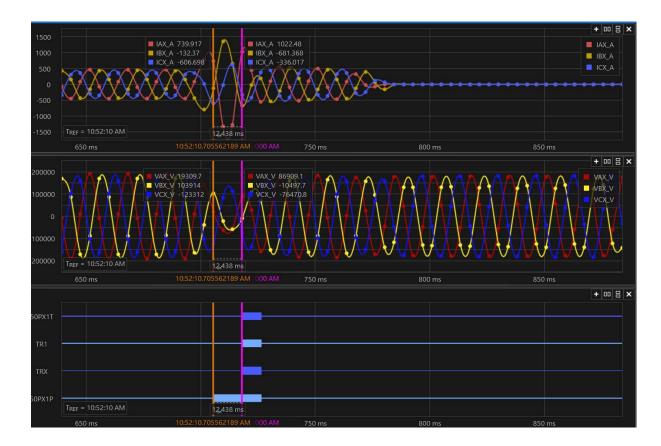

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.7<br>6.3.7<br>6.3.7                                                                                           | ER SIX<br>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br>GENERATOR<br>Introduction<br>IEEE 9-Bus system<br>The hardware in the loop simulation test-bed implementation for a generator protection<br>res<br>1 The implementation of hardware in the loop test-bed for generator volts per hertz<br>ection scheme using SEL 700G IED<br>2 Hardware in the loop simulation results for over excitation condition | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126<br>. 129<br>t                                              |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.7<br>6.3.7<br>6.3.7                                                                                           | <ul> <li>ER SIX</li> <li>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br/>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br/>GENERATOR</li></ul>                                                                                                                                                                                                                                                                                                                  | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126<br>. 129<br>t<br>. 131                                     |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.1<br>6.3.1<br>6.3.1<br>6.3.1<br>6.3.1<br>6.3.1                                                                | <ul> <li>ER SIX</li> <li>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br/>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br/>SENERATOR</li></ul>                                                                                                                                                                                                                                                                                                                  | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126<br>. 129<br>t<br>. 131<br>. 133                            |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.1<br>6.3.1<br>6.3.1<br>6.3.1<br>6.3.1<br>6.3.1                                                                | <ul> <li>ER SIX</li> <li>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br/>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br/>BENERATOR</li></ul>                                                                                                                                                                                                                                                                                                                  | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126<br>. 129<br>t<br>. 131<br>. 133<br>. 135                   |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.3<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4 | <ul> <li>R SIX</li> <li>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br/>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br/>GENERATOR</li></ul>                                                                                                                                                                                                                                                                                                                   | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126<br>. 129<br>t<br>. 131<br>. 133<br>. 135<br>. 135          |

| CHAPTE<br>IMPLEM<br>HERTZ,<br>FOR A G<br>6.1<br>6.2<br>6.3<br>schem<br>6.3.3<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4<br>prote<br>6.3.4 | <ul> <li>R SIX</li> <li>ENTATION OF THE HARDWARE-IN-THE-LOOP SIMULATION TO TEST VOLTS PER<br/>A BACK UP OVERCURRENT, OVER AND UNDER VOLTAGE PROTECTION SCHEME<br/>SENERATOR</li></ul>                                                                                                                                                                                                                                                                                                                   | . 123<br>S<br>. 123<br>. 123<br>. 124<br>. 125<br>. 126<br>. 129<br>t<br>. 131<br>. 133<br>. 135<br>. 135<br>. 136 |

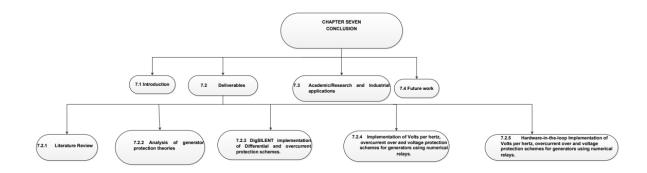

| CHAPTE         | R SEVEN                                                                                                                                      | 139 |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CONCLU         | JSION                                                                                                                                        | 139 |

| 7.1            | Introduction                                                                                                                                 | 139 |

| 7.2            | Deliverables                                                                                                                                 | 140 |

| 7.2.1          | 1 Literature Review                                                                                                                          | 140 |

| 7.2.2          | 2 Analysis of generator protection theories                                                                                                  | 140 |

| 7.2.3          | 3 DigSILENT implementation of Differential and overcurrent protection schemes                                                                | 140 |

| 7.2.4<br>gene  | 4 Implementation of Volts per hertz, overcurrent over and voltage protection schemes fo<br>erators using numerical relays.                   |     |

| 7.2.8<br>prote | 5 Hardware-in-the-loop Implementation of Volts per hertz, overcurrent over and voltage ection schemes for generators using numerical relays. | 141 |

| 7.3            | Academic/Research and Industrial applications                                                                                                | 141 |

| 7.4            | Future work                                                                                                                                  | 141 |

| BIBLIOG        | RAPHY                                                                                                                                        | 142 |

| APPEND         | DICES                                                                                                                                        | 145 |

| A.1            | Introduction                                                                                                                                 | 123 |

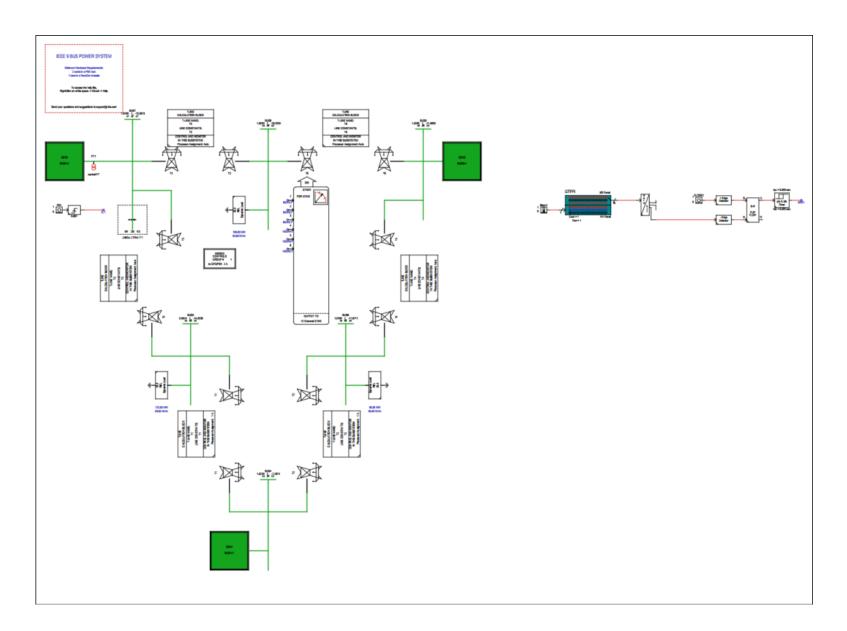

| A.2            | IEEE 9-Bus system                                                                                                                            | 123 |

| A.2.           | 1 Transformer data                                                                                                                           | 124 |

| A.2.           | 2 Load data                                                                                                                                  | 124 |

| A.2.           | 3 Generator data                                                                                                                             | 124 |

| A.2.4          | 4 Transmission line data                                                                                                                     | 125 |

| A.3            | IEEE 9-Bus system in RSCAD environment                                                                                                       | 125 |

| B.1            | Introduction                                                                                                                                 | 127 |

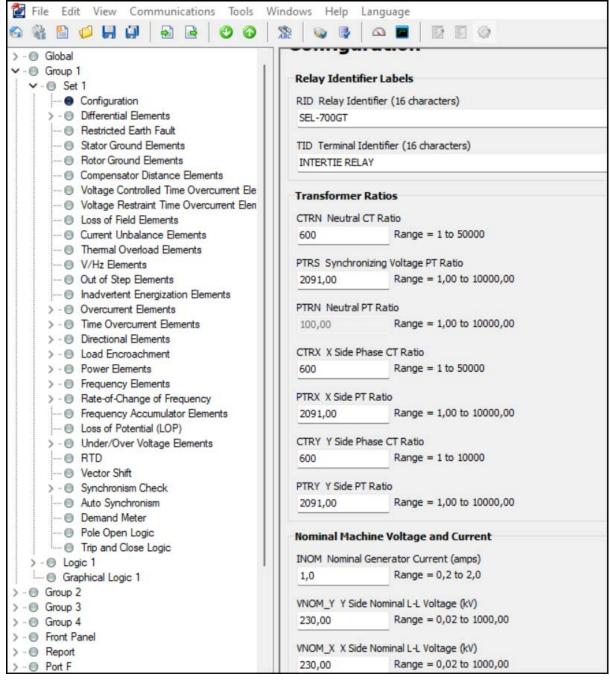

| B.1.           | 1 SEL 700G Device Information                                                                                                                | 127 |

| B.1.           | 2 Port configuration setting of SEL 700G                                                                                                     | 127 |

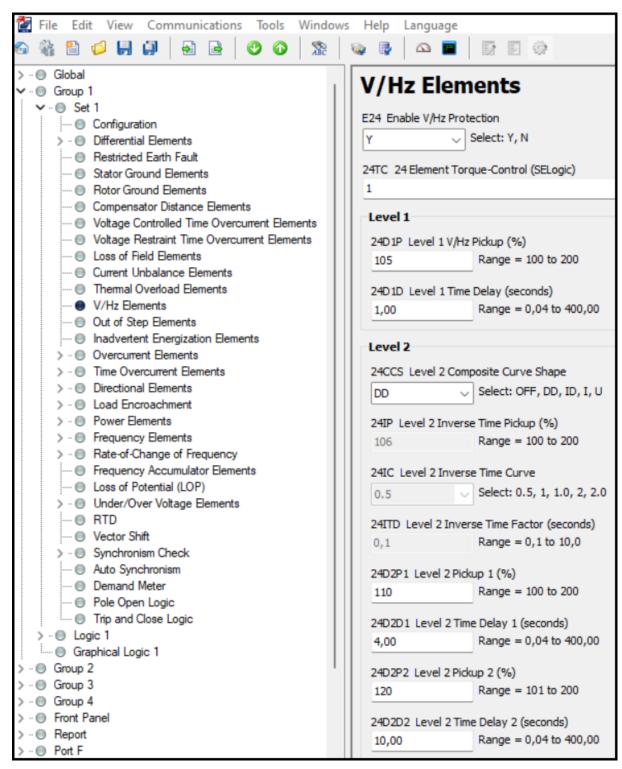

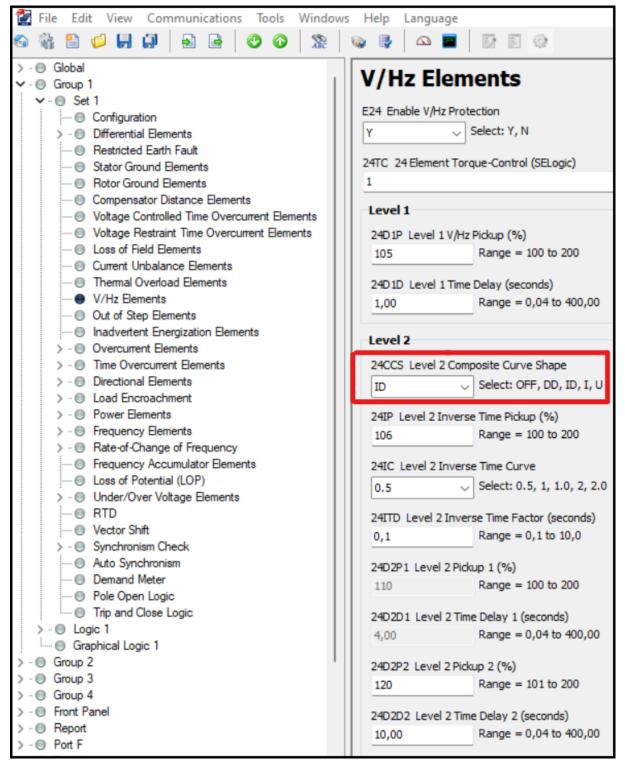

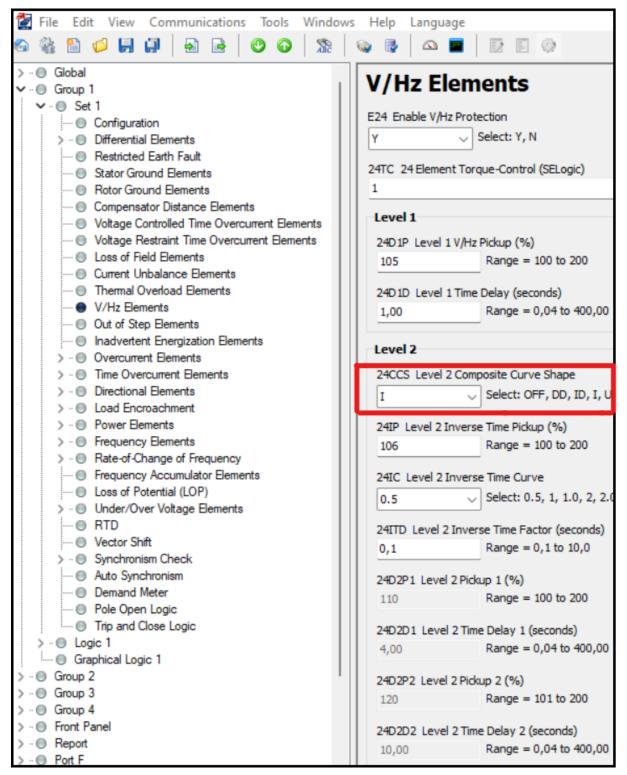

| B.1.           | 3 Volts per hertz element configuration setting                                                                                              | 128 |

| B.1.4          | 4 output configuration setting of volts per hertz setting                                                                                    | 129 |

## LIST OF FIGURES

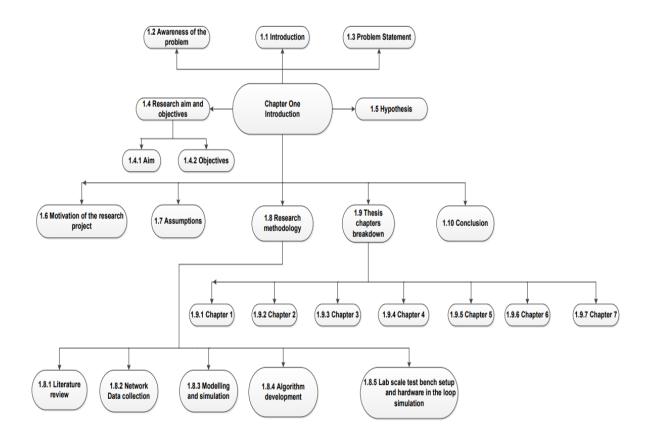

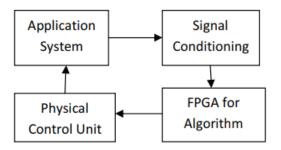

| Figure 1.0: Summary of the content covered in chapter one                                           | 2  |

|-----------------------------------------------------------------------------------------------------|----|

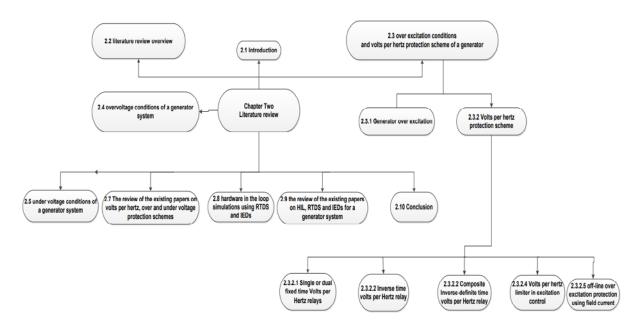

| Figure 2.0: Summary of the content covered in chapter two                                           |    |

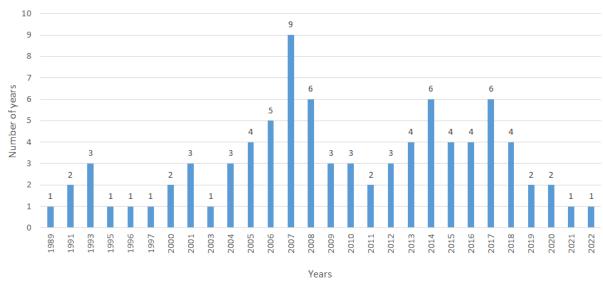

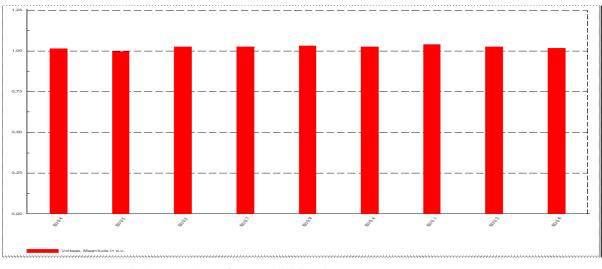

| Figure 2.1: Publication reviewed per year                                                           |    |

|                                                                                                     |    |

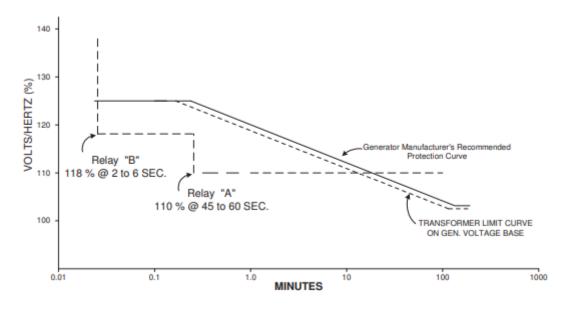

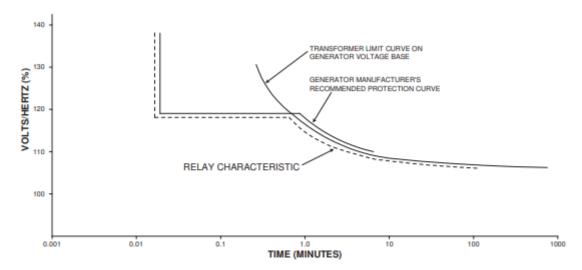

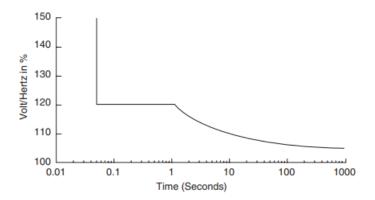

| Figure 2.2: Setting for dual fixed time V/Hz relays (Power and Society, 2005).                      |    |

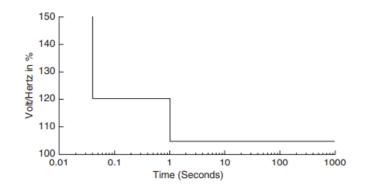

| Figure 2.3: Setting for inverse-define time volts per hertz relay (Power and Society, 2005).        |    |

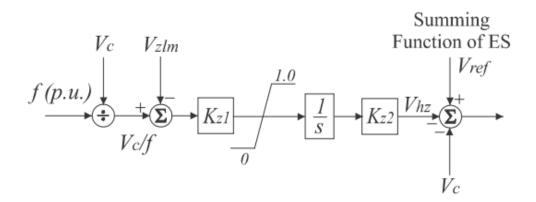

| Figure 2.4: Dynamic Model of an Over-excitation Limiter(Piardi <i>et al.</i> , 2013)                |    |

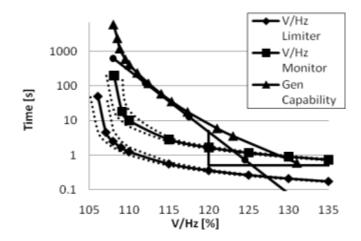

| Figure 2.5: V/Hz Limiter, generator capability and protection settings(Kharel <i>et al.</i> , 2010) |    |

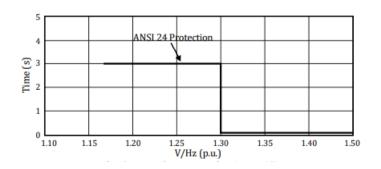

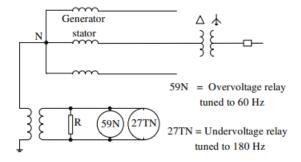

| Figure 2.6: Overvoltage protection (ANSI 59)(Baracho et al., 2021)                                  |    |

| Figure 2.8: Hardware in the loop in the RTDS(Coelho et al., 2015)                                   |    |

| Figure 3.0: the summary of the content covered in chapter three                                     | 27 |

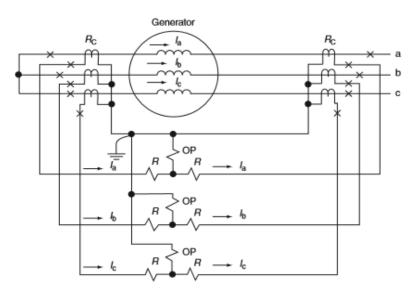

| Figure 3.1: Generator protection scheme(Leonard L. Grigsby, 2007)                                   | 28 |

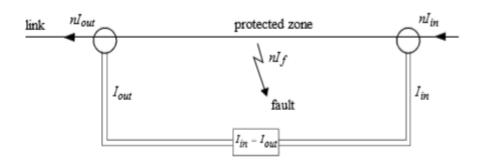

| Figure 3.2: A Typical differential protection scheme diagram(Prévé, 2006)                           | 29 |

| Figure 3.3: A typical differential scheme connection (Blackburn JL and Domin JT, 2006)              | 29 |

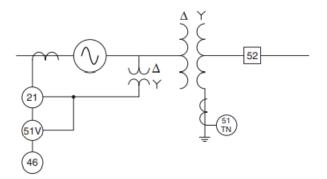

| Figure 3.3: Backup protection basic scheme(Leonard L. Grigsby, 2007)                                | 30 |

| Figure 3.4: Voltage restraint overcurrent relay(Leonard L. Grigsby, 2007)                           |    |

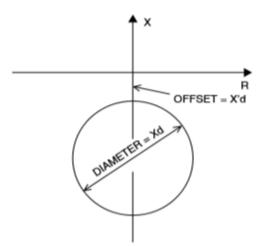

| Figure 3.5: A typical mho relay characteristics (Leonard L. Grigsby, 2007)                          |    |

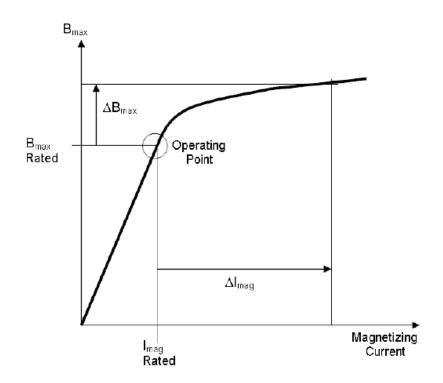

| Figure 3.6: A typical saturated curve (I. Kerszenbaum and G. Klempner, 2008)                        |    |

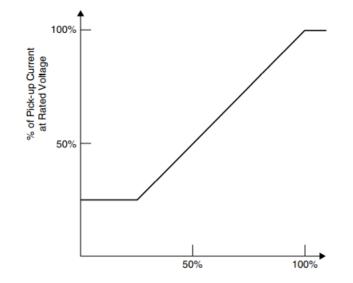

| Figure 3.7: Combined definite and inverse characteristics(Leonard L. Grigsby, 2007)                 |    |

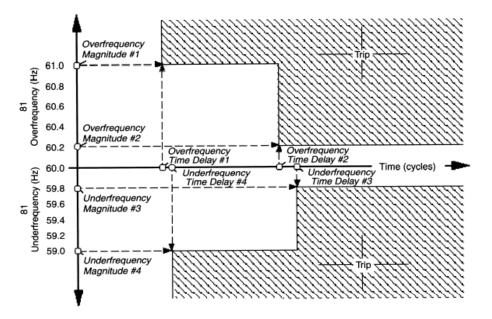

| Figure 3.8: Dual level characteristics(Leonard L. Grigsby, 2007)                                    |    |

| Figure 3.9: Over and under voltage protection scheme(Ibrahim, 2011)                                 |    |

| Figure 3.10: Basic over and under frequency region of operation and protective settings(I.          | 00 |

| Kerszenbaum and G. Klempner, 2008)                                                                  | 36 |

| Figure 4.0: Summary of the content covered in Chapter four                                          |    |

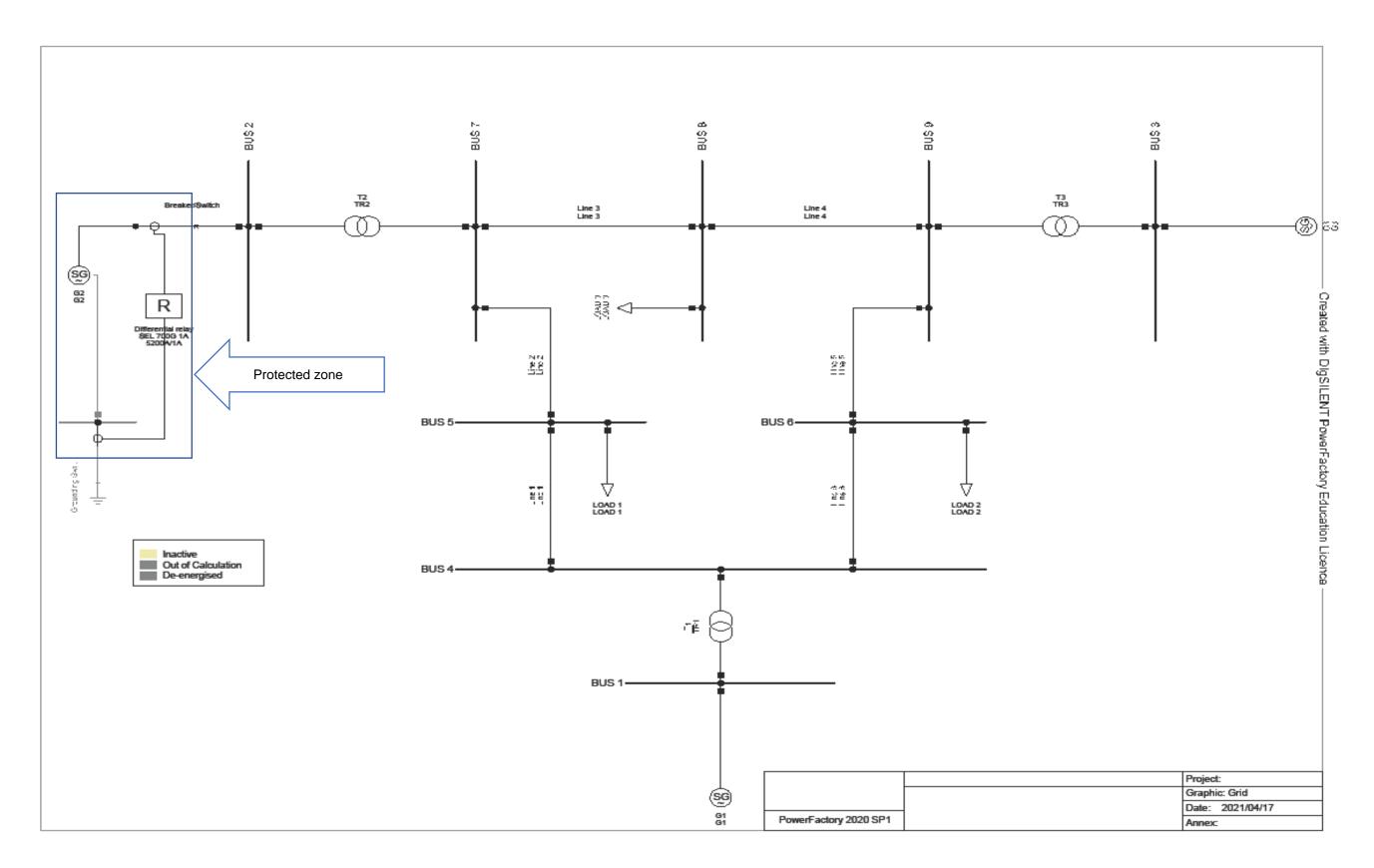

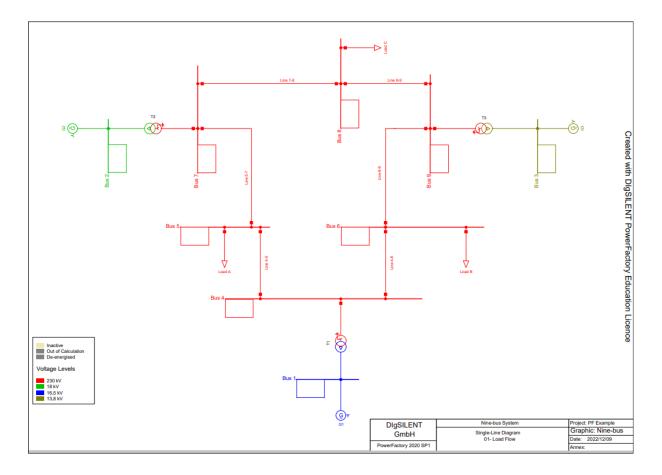

| Figure 4.1: IEEE 9 Bus system single line diagram                                                   |    |

| Figure 4.3: Typical voltage for the IEEE 9-Bus network                                              |    |

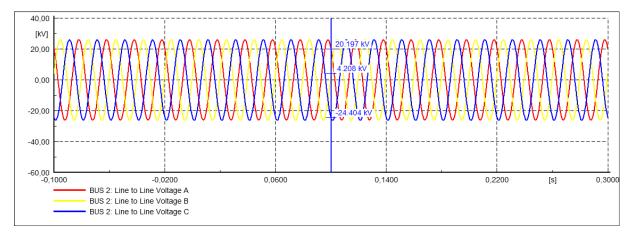

| Figure 4.4: Three phase voltages at bus 2 of IEEE9-Bus system                                       | 40 |

| Figure 4.5: Different types of short circuit in a three phase network(IEC International             |    |

| Standard 90909, 2001)                                                                               | 15 |

| Figure 4.6: IEEE 9 Bus network in a DigSILENT simulation environment                                |    |

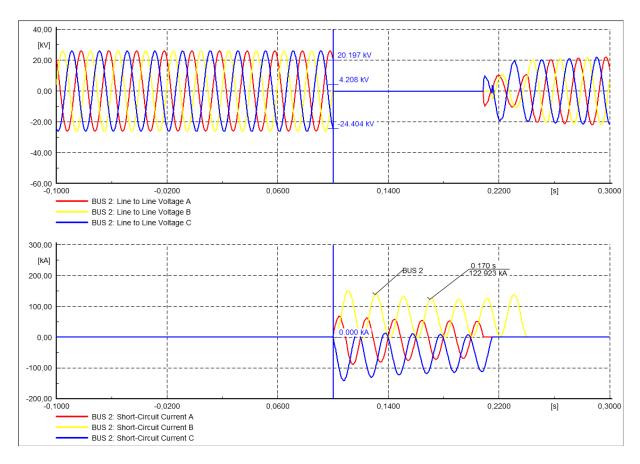

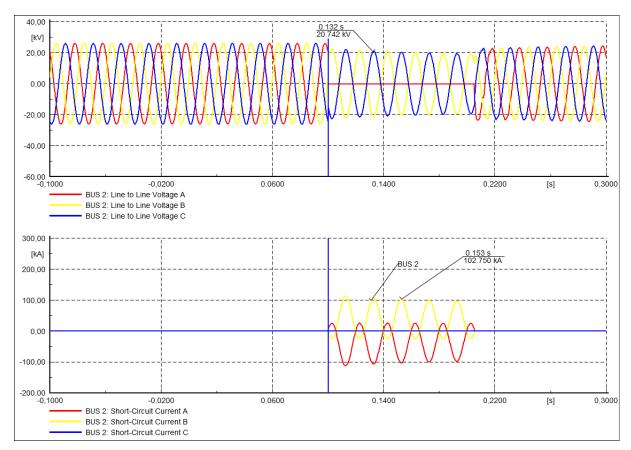

| Figure 4.7: Voltage and current Plots for 3ph internal fault at Bus 2                               |    |

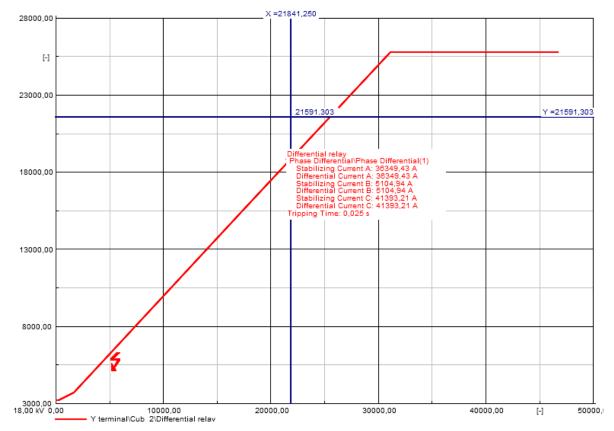

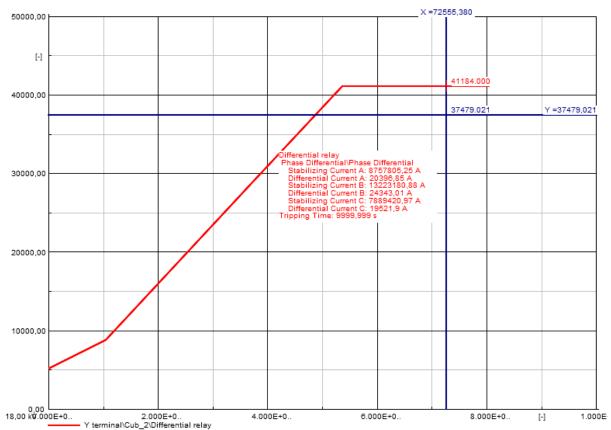

| Figure 4.8: Current comparison differential plots for three phase internal fault                    |    |

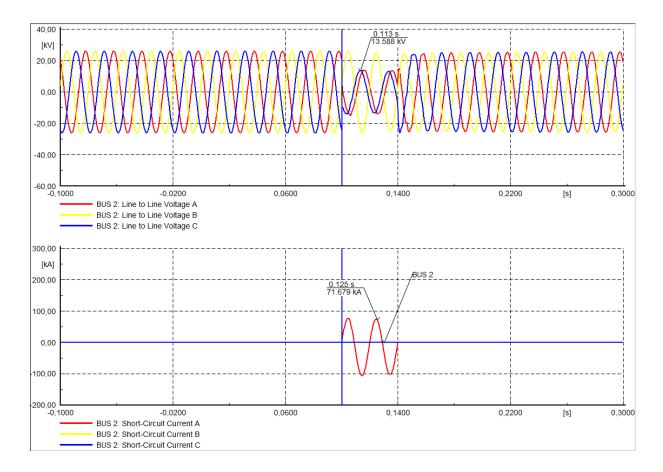

| Figure 4.9: Voltage and current Plots for single phase to ground at Bus 2                           |    |

|                                                                                                     |    |

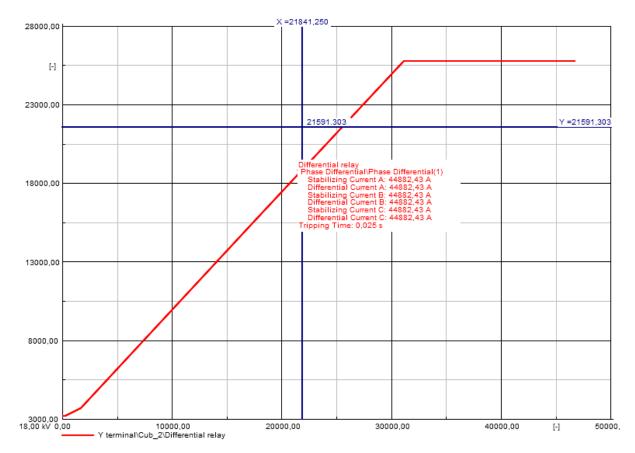

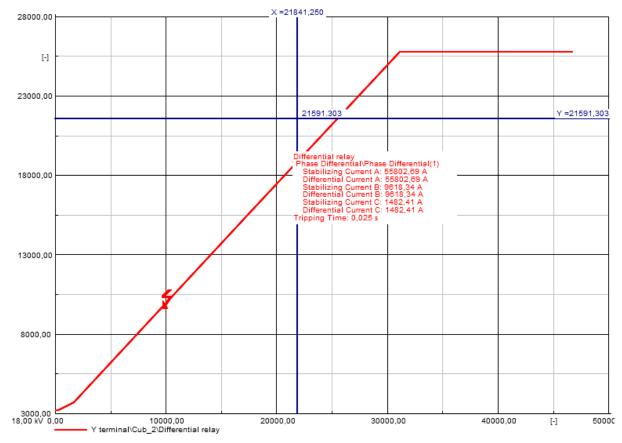

| Figure 4.10: Current comparison differential plots for single phase to ground internal fault.       |    |

| Figure 4.11: Voltage and current Plots for two phase internal fault                                 |    |

| Figure 4.12: Current comparison differential plots for two phase internal fault                     |    |

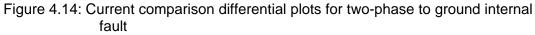

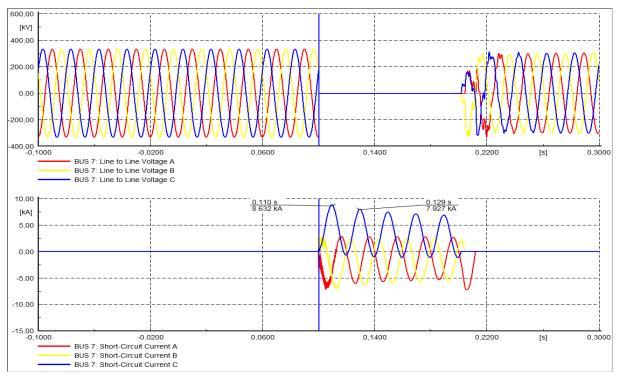

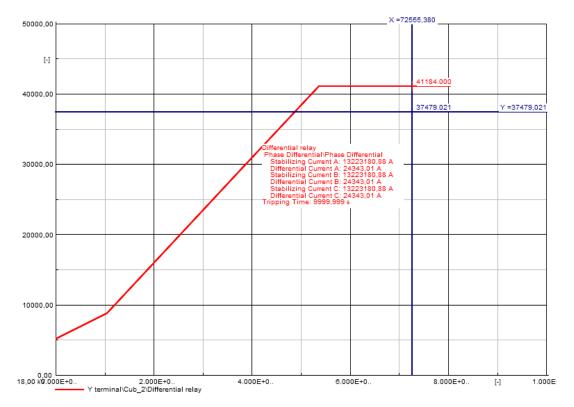

| Figure 4.13: Voltage and current Plots for two-phase to ground internal fault                       |    |

| Figure 4.14: Current comparison differential plots for two-phase to ground internal fault           |    |

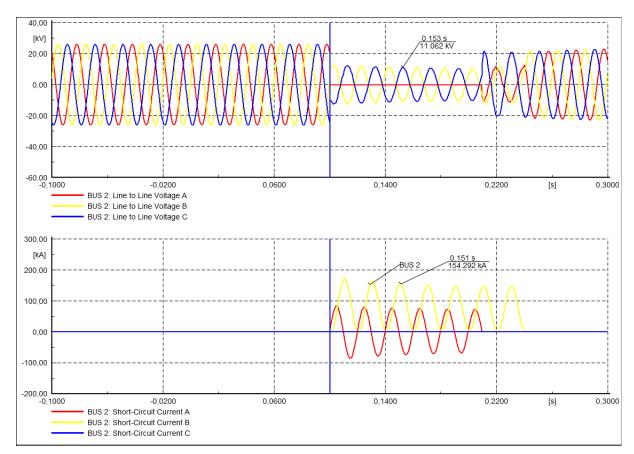

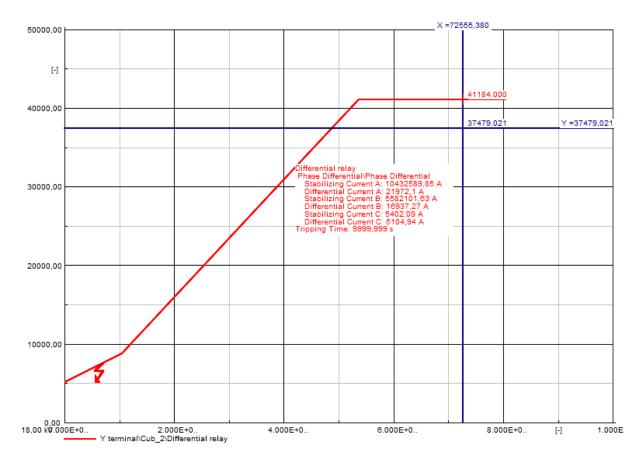

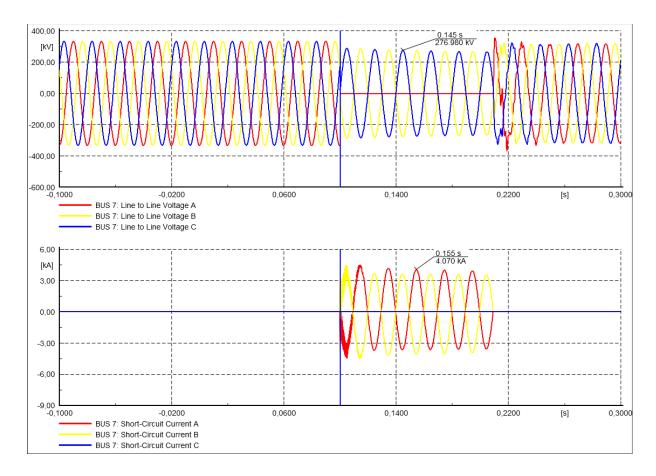

| Figure 4.15: Voltage and current Plots for 3ph external fault at Bus 7                              |    |

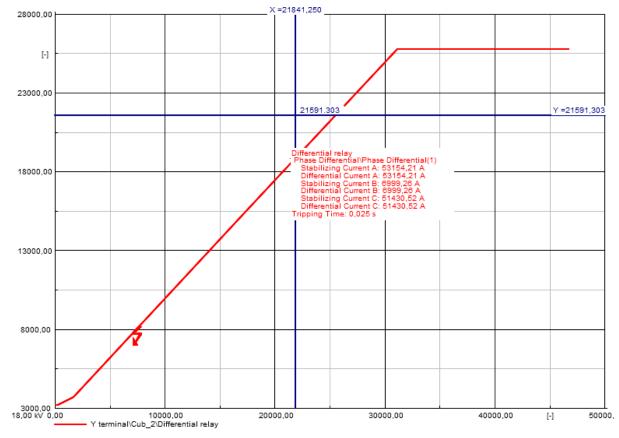

| Figure 4.16: Current comparison differential plots for three phase external fault                   |    |

| Figure 4.17: Voltage and current Plots for single phase to ground fault at Bus 7                    |    |

| Figure 4.18: Current comparison differential plots for single phase to ground external fault.       |    |

| Figure 4.19: Voltage and current Plots for two phase external fault at Bus 7                        |    |

| Figure 4.20: Current comparison differential plots for two-phase external fault                     |    |

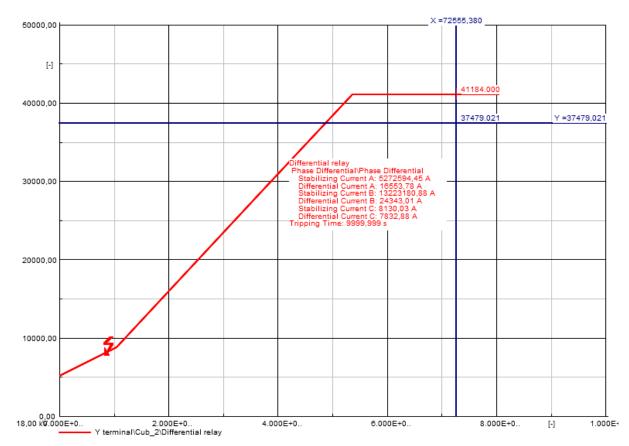

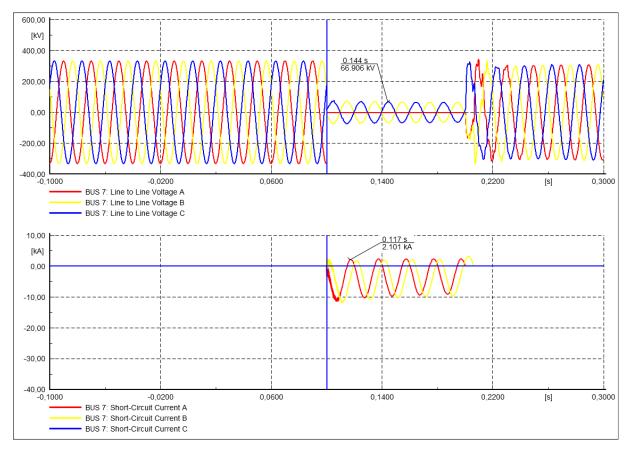

| Figure 4.21: Voltage and current Plots for two-phase to ground external fault                       |    |

| Figure 4.22: Current comparison differential plots for two-phase to ground external fault           |    |

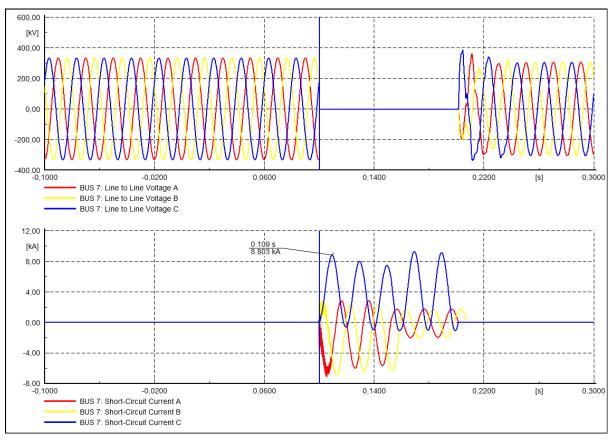

| Figure 4.23: Voltage and Current signals for three phase fault at Bus 7                             |    |

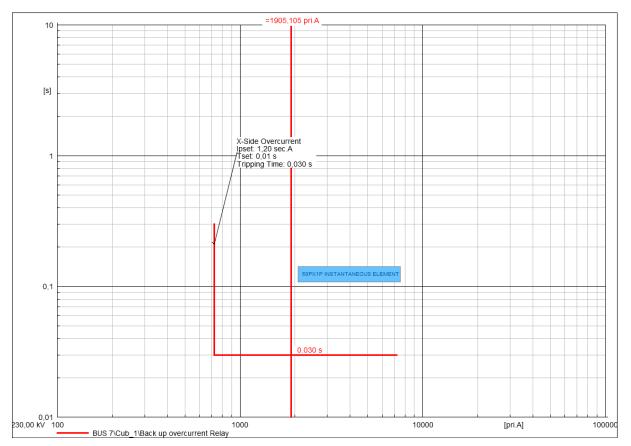

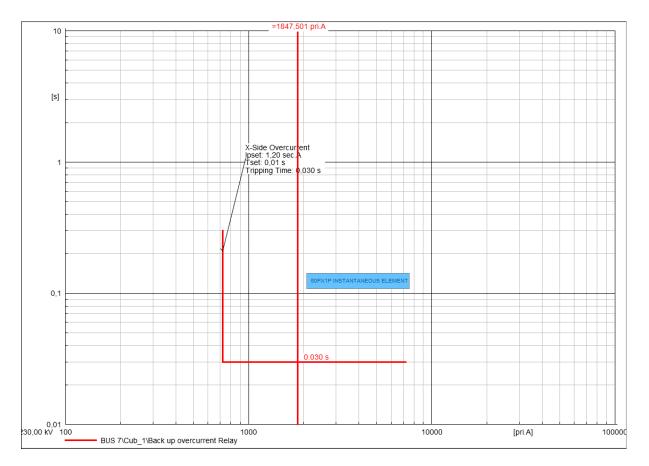

| Figure 4.24: Time overcurrent curve for SEL700G relay response to three phase fault                 |    |

| Figure 4.25: Voltage and Current signals for a single phase to ground fault at Bus 7                | 71 |

| Figure 4.26: Time overcurrent curve for SEL700G relay response for single phase to groun            | d  |

| fault                                                                                               |    |

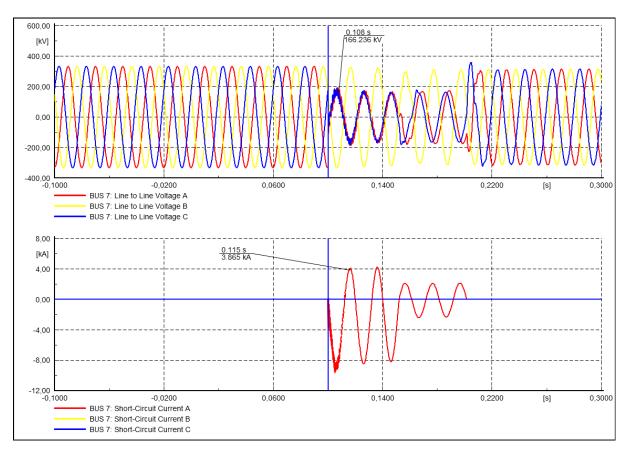

| Figure 4.27: Voltage and Current signals for double phase to ground fault at Bus 7                  | 73 |

| Figure 4.28: Time overcurrent curve for SEL700G relay response for double phase to grour            |    |

| fault                                                                                               | 74 |

| Figure 4.29: Voltage and Current signals for double phase to ground fault at Bus 7                  | 75 |

| Figure 4.30: Time overcurrent curve for SEL700G relay response for two phase fault                                                                                                                                                                                                                              |                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

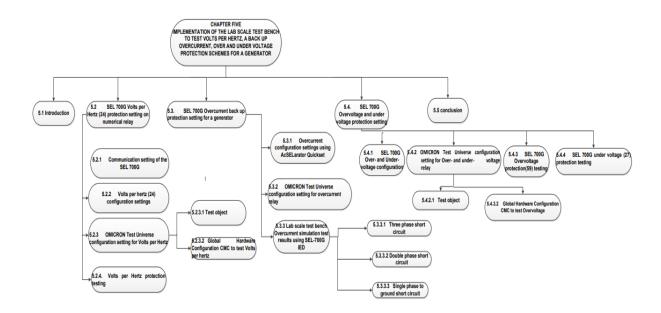

| Figure 5.0: The summary of the content found in chapter five                                                                                                                                                                                                                                                    |                                |

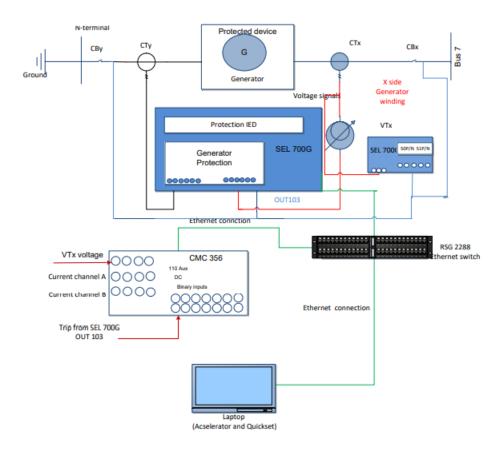

| Figure 5.1: Volts per hertz (24) lab-scale test bench setup                                                                                                                                                                                                                                                     |                                |

| Figure 5.2: SEL 700G communication parameter setting on AcSELarator                                                                                                                                                                                                                                             |                                |

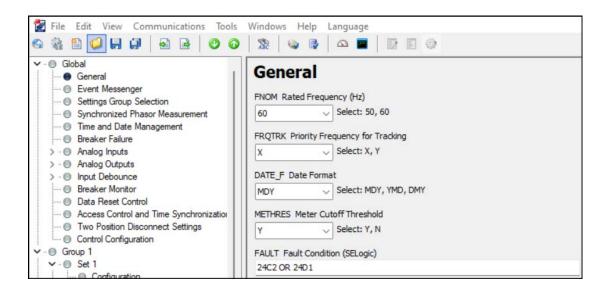

| Figure 5.3: General setting of SEL700G IED on AcSELarator Quickset                                                                                                                                                                                                                                              |                                |

| Figure 5.4: Instrument transformer ratio and nominal machine settings                                                                                                                                                                                                                                           |                                |

| Figure 5.5: Volts per hertz configuration setting (24CCS=DD) in AcSELarator Quickset                                                                                                                                                                                                                            |                                |

| Figure 5.7: Volts per hertz configuration setting (24CCS=I) in AcSELarator Quickset                                                                                                                                                                                                                             |                                |

| Figure 5.8: Trip and close logic configuration setting for V/Hz elements                                                                                                                                                                                                                                        |                                |

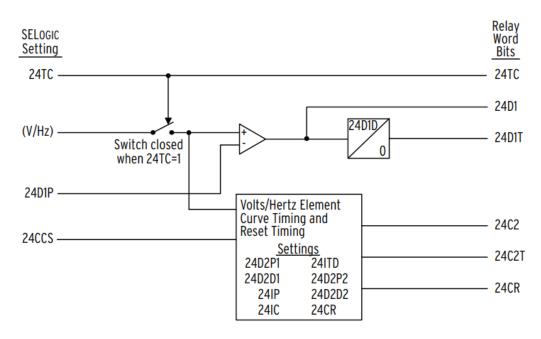

| Figure 5.9: Volts per hertz trip logic (SEL Relay Manual, 2018)                                                                                                                                                                                                                                                 |                                |

| Figure 5.10: Defining the Test Object for SEL 700G on Test Universe software                                                                                                                                                                                                                                    |                                |

| Figure 5.11: SEL700 Device settings on test universe                                                                                                                                                                                                                                                            |                                |

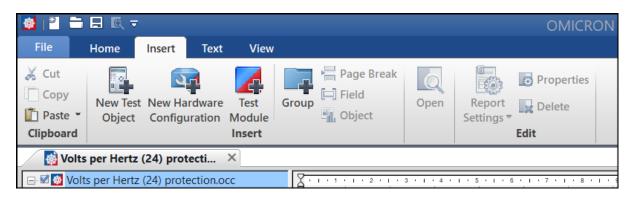

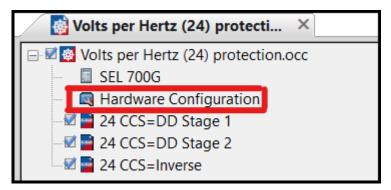

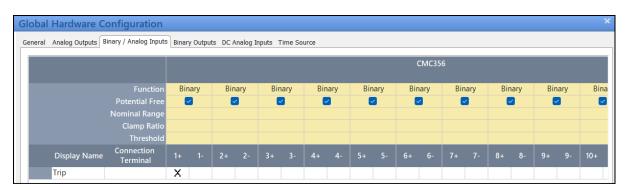

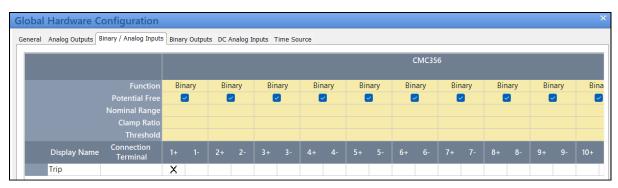

| Figure 5.12: Global Hardware Configuration CMC to test Volts per hertz                                                                                                                                                                                                                                          |                                |

| Figure 5.13: Output configuration of volts per hertz protection                                                                                                                                                                                                                                                 |                                |

| Figure 5.14: Analogue output of the volts per hertz relay                                                                                                                                                                                                                                                       |                                |

| Figure 5.15: The trip signal of the volts per hertz protection scheme                                                                                                                                                                                                                                           |                                |

| Figure 5.16: Nominal state and faults state values for DD stage 1                                                                                                                                                                                                                                               |                                |

| Figure 5.17: The detailed view of the fault condition for DD stage 1                                                                                                                                                                                                                                            |                                |

| Figure 5.18: The state termination for DD stage 1                                                                                                                                                                                                                                                               |                                |

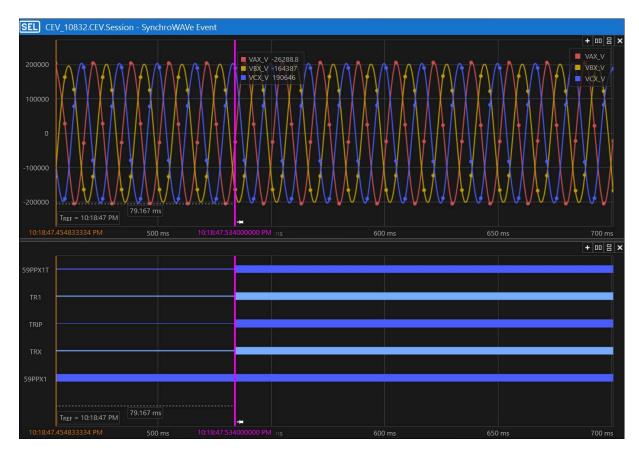

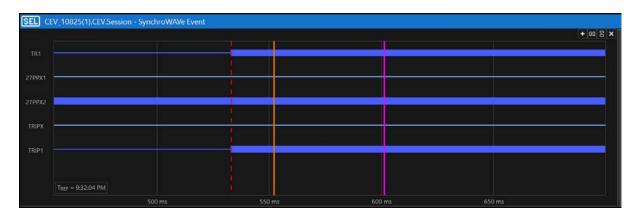

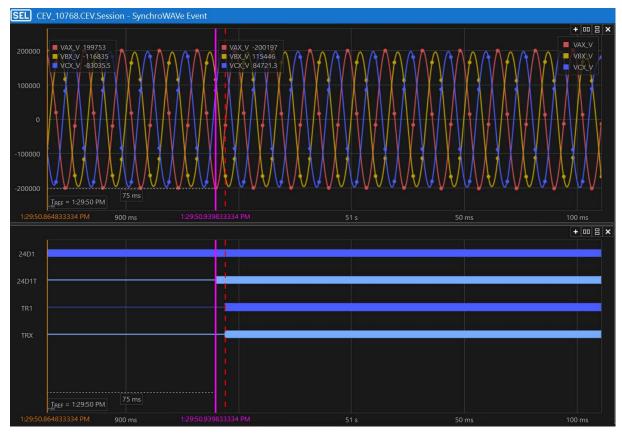

| Figure 5.19: DD Event report file on Synchro event wave                                                                                                                                                                                                                                                         |                                |

| Figure 5.20: Phase to phase voltage and digital signals of the SEL 700G IED at V/Hz lev                                                                                                                                                                                                                         | /el                            |

| 110%<br>Figure 5.21: Nominal state and faults state values for DD stage 2                                                                                                                                                                                                                                       | 90<br>90                       |

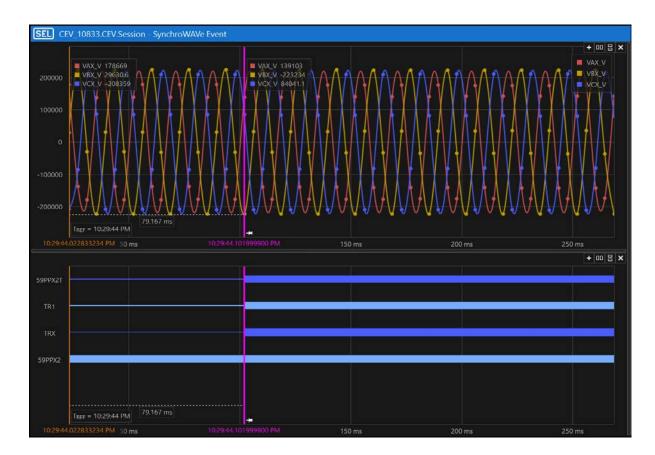

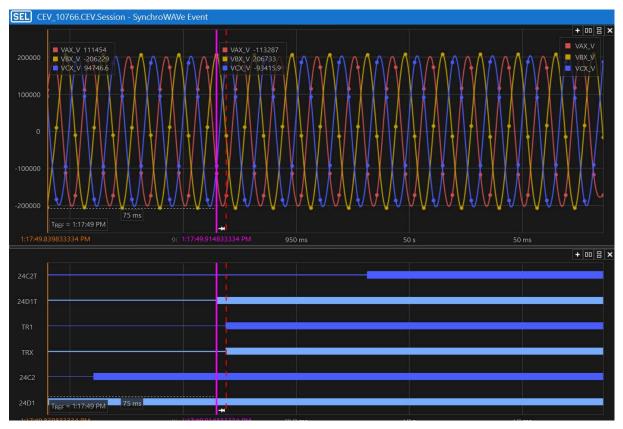

| Figure 5.22: Phase to phase voltages and trip signals of the SEL 700G at V/Hz level of 1                                                                                                                                                                                                                        |                                |

|                                                                                                                                                                                                                                                                                                                 |                                |

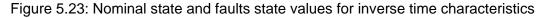

| Figure 5.23: Nominal state and faults state values for inverse time characteristics                                                                                                                                                                                                                             |                                |

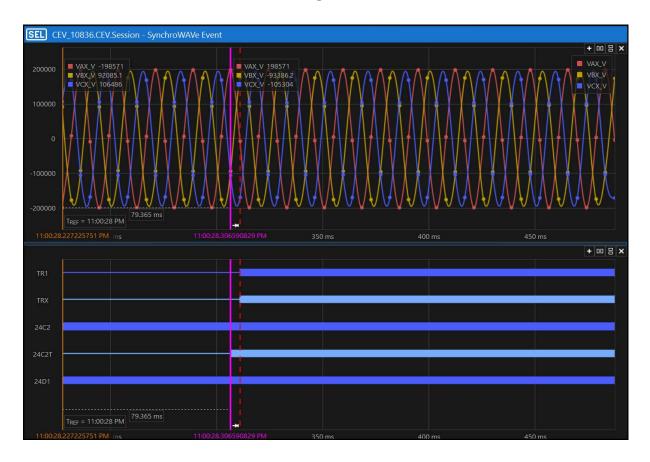

| Figure 5.24: Phase to phase voltages, frequency and trip signals of the SEL 700G IEI                                                                                                                                                                                                                            |                                |

| inverse time characteristics                                                                                                                                                                                                                                                                                    |                                |

| Figure 5.25: General settings of SEL 700G overcurrent relay                                                                                                                                                                                                                                                     |                                |

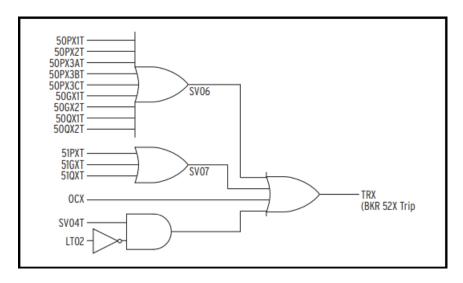

| Figure 5.26: SEL 700G Trip logic Diagram(SEL Relay Manual, 2018)                                                                                                                                                                                                                                                | 101                            |

| Figure 5.27: SEL 700G device setting in the Test Universe                                                                                                                                                                                                                                                       |                                |

| Figure 5.28: Overcurrent relay parameters                                                                                                                                                                                                                                                                       |                                |

| Figure 5.29: Overcurrent relay parameters                                                                                                                                                                                                                                                                       |                                |

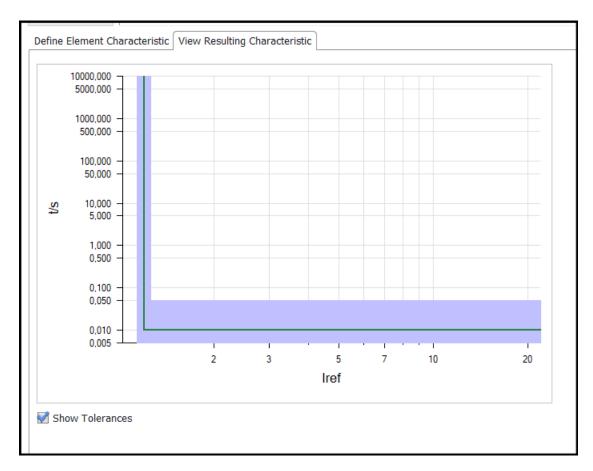

| Figure 5.30: Phase overcurrent curve on Test Universe                                                                                                                                                                                                                                                           |                                |

| Figure 5.31: Global Hardware Configuration on Test Universe                                                                                                                                                                                                                                                     |                                |

| Figure 5.32: Current channel A output configuration settings of CMC 356 device                                                                                                                                                                                                                                  | 105                            |

| Figure 5.33: Analog output configuration settings of SEL 700G                                                                                                                                                                                                                                                   |                                |

| Figure 5.34: Binary inputs configuration settings of SEL 700G                                                                                                                                                                                                                                                   |                                |

| Figure 5.35: Trip time characteristics test tab                                                                                                                                                                                                                                                                 |                                |

| Figure 5.36: Three phase fault signals of SEL700G overcurrent relay                                                                                                                                                                                                                                             | 107                            |

| Figure 5.37: Double phase fault signals of SEL700G overcurrent relay                                                                                                                                                                                                                                            |                                |

| Figure 5.38: Single phase fault signals of SEL700G overcurrent relay                                                                                                                                                                                                                                            |                                |

| Figure 5.39: General setting of SEL 700G Over- and Under-voltage Protection relay                                                                                                                                                                                                                               |                                |

| Figure 5.40: Overvoltage logic (SEL Relay Manual, 2018)                                                                                                                                                                                                                                                         |                                |

| Figure 5.41: Under-voltage logic (SEL Relay Manual, 2018)                                                                                                                                                                                                                                                       |                                |

| Figure 5.42: Test object settings of over- and under-voltage relay                                                                                                                                                                                                                                              |                                |

| Figure 5.43: Global hardware configuration setting of over- and under-voltage relay                                                                                                                                                                                                                             |                                |

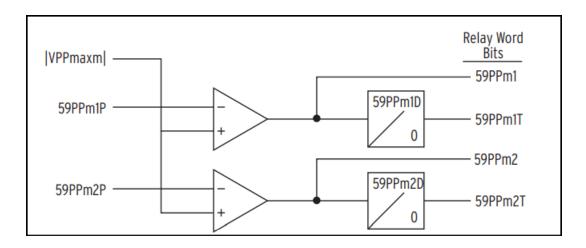

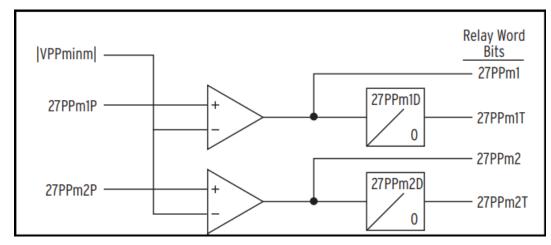

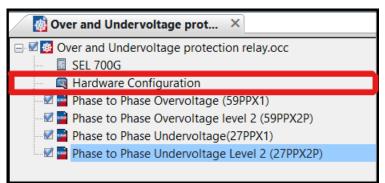

| Figure 5.44: Analogue output of the over-and under-voltage relay                                                                                                                                                                                                                                                |                                |

| Figure 5.45: Output configuration of over- and under-voltage protection                                                                                                                                                                                                                                         |                                |

|                                                                                                                                                                                                                                                                                                                 |                                |

| Figure 5.46. The thd signal of the over- and under-voltage protection scheme                                                                                                                                                                                                                                    |                                |

| Figure 5.46: The trip signal of the over- and under-voltage protection scheme<br>Figure 5.47: Test view of overvoltage protection relay stage 1                                                                                                                                                                 |                                |

| Figure 5.47: Test view of overvoltage protection relay stage 1                                                                                                                                                                                                                                                  | 115                            |

| Figure 5.47: Test view of overvoltage protection relay stage 1<br>Figure 5.48: The state termination for over- and under-voltage relay                                                                                                                                                                          | 115<br>116                     |

| Figure 5.47: Test view of overvoltage protection relay stage 1                                                                                                                                                                                                                                                  | 115<br>116<br>ay               |

| Figure 5.47: Test view of overvoltage protection relay stage 1<br>Figure 5.48: The state termination for over- and under-voltage relay<br>Figure 5.49: Phase to phase voltages and trip signals of the SEL 700G over voltages rel<br>(5PPX1P)<br>Figure 5.50: Test view of overvoltage protection relay stage 2 | 115<br>116<br>ay<br>117<br>117 |

| Figure 5.47: Test view of overvoltage protection relay stage 1<br>Figure 5.48: The state termination for over- and under-voltage relay<br>Figure 5.49: Phase to phase voltages and trip signals of the SEL 700G over voltages rel<br>(5PPX1P)                                                                   | 115<br>116<br>ay<br>117<br>117 |

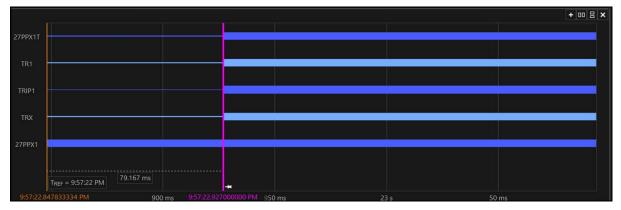

| Figure 5.52: Test view of under voltage protection relay stage 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Figure 5.53: Trip signals of the SEL 700G under voltages relay (27PPX1P).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120                                                         |

| Figure 5.54: Test view of under voltage protection relay stage 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |

| Figure 5.55: Prip signals of the SEL 700G under voltages relay (27PPX2P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 121                                                         |

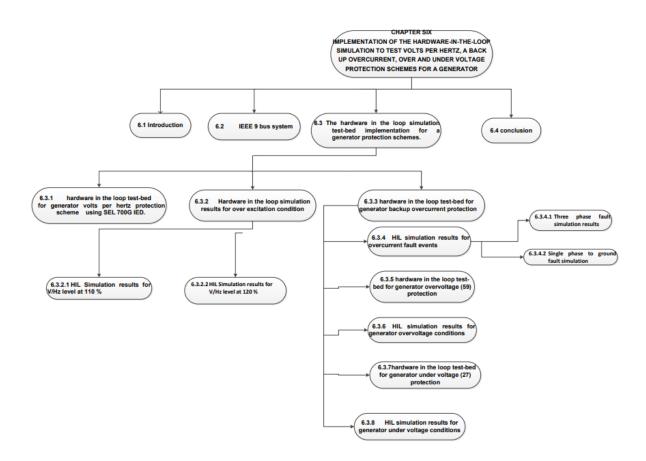

| Figure 6.0: Summary of the content covered in Chapter six                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 124                                                         |

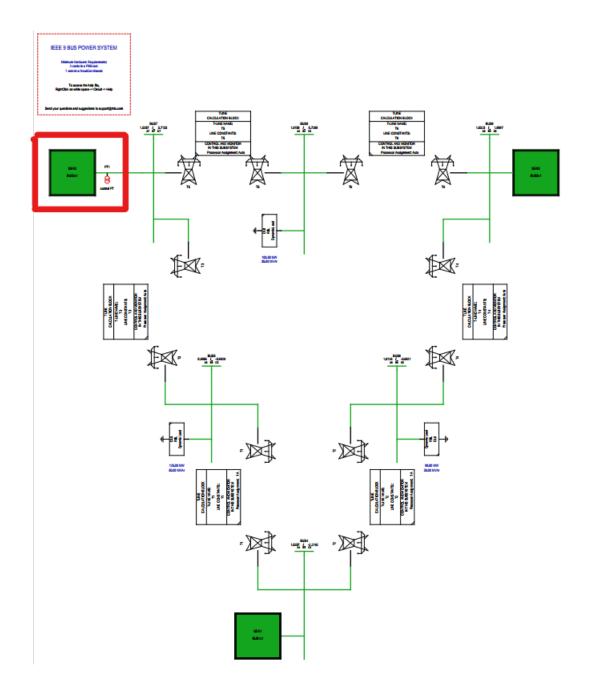

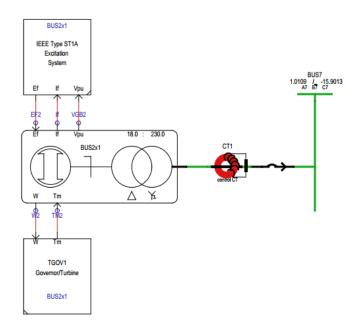

| Figure 6.1: IEEE 9-Bus system on RSCAD Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

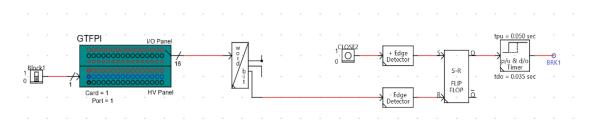

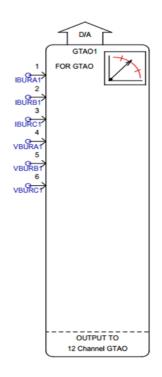

| Figure 6.2: DAC component on RSCAD Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 126                                                         |

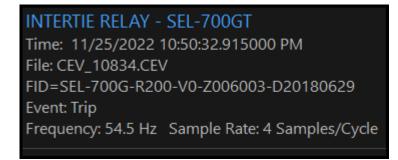

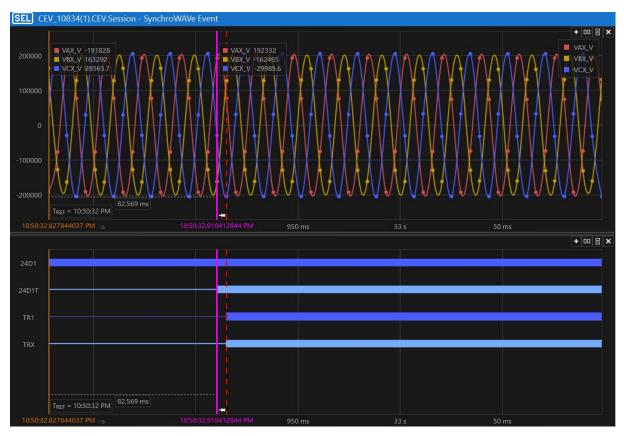

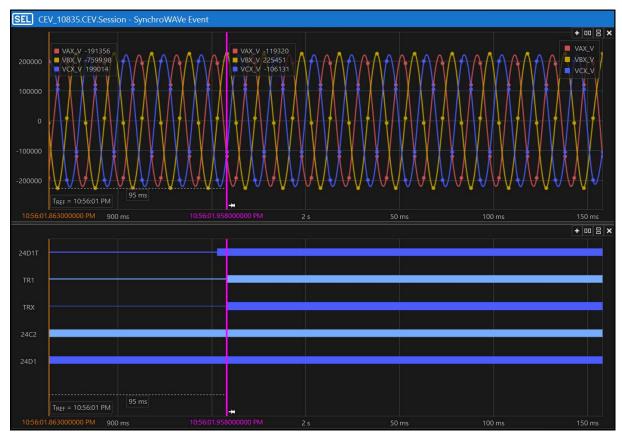

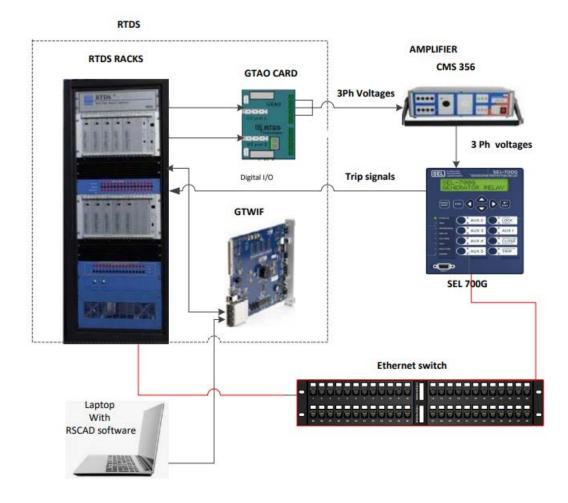

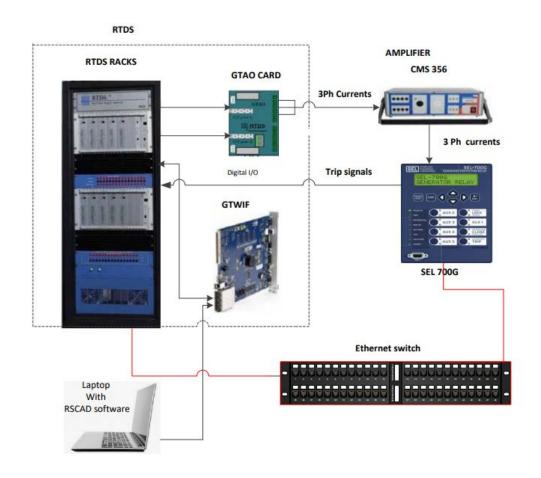

| Figure 6.3: Hardware in the loop test bed for volts per hertz protection scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128                                                         |